DLPC2607 DLP PICO Processor 2607 ASIC (Rev. C)0 pages

Product

Folder

Sample &

Buy

Support &

Community

Tools &

Software

Technical

Documents

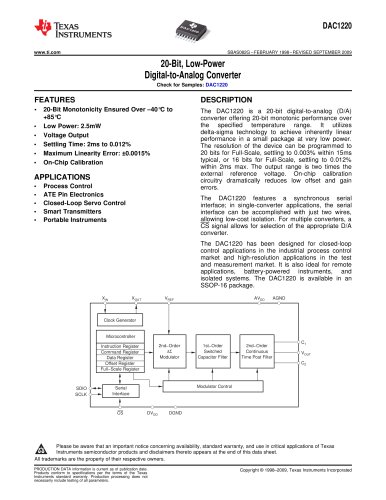

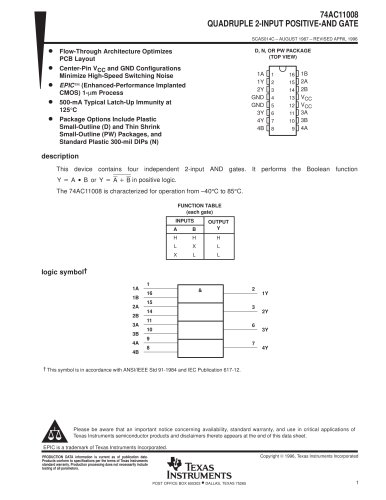

DLPC2607

DLPS030C – DECEMBER 2013 – REVISED NOVEMBER 2015

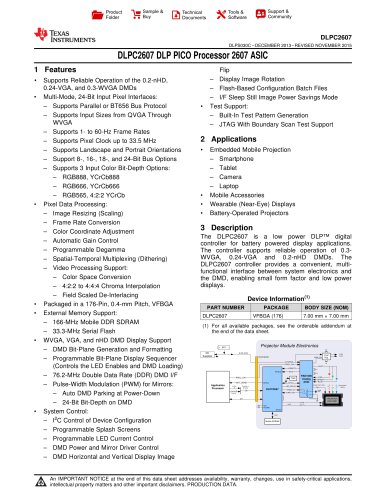

DLPC2607 DLP PICO Processor 2607 ASIC

1 Features

•

•

•

•

•

•

2 Applications

•

•

•

•

Embedded Mobile Projection

– Smartphone

– Tablet

– Camera

– Laptop

Mobile Accessories

Wearable (Near-Eye) Displays

Battery-Operated Projectors

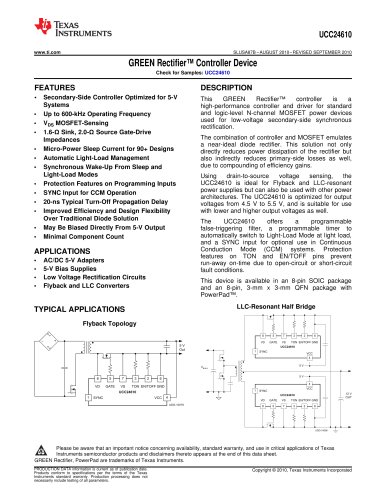

3 Description

The DLPC2607 is a low power DLP™ digital

controller for battery powered display applications.

The controller supports reliable operation of 0.3WVGA, 0.24-VGA and 0.2-nHD DMDs. The

DLPC2607 controller provides a convenient, multifunctional interface between system electronics and

the DMD, enabling small form factor and low power

displays.

Device Information(1)

PART NUMBER

PACKAGE

DLPC2607

BODY SIZE (NOM)

VFBGA (176)

7.00 mm × 7.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

BAT

Projector Module Electronics

±

•

Supports Reliable Operation of the 0.2-nHD,

0.24-VGA, and 0.3-WVGA DMDs

Multi-Mode, 24-Bit Input Pixel Interfaces:

– Supports Parallel or BT656 Bus Protocol

– Supports Input Sizes from QVGA Through

WVGA

– Supports 1- to 60-Hz Frame Rates

– Supports Pixel Clock up to 33.5 MHz

– Supports Landscape and Portrait Orientations

– Support 8-, 16-, 18-, and 24-Bit Bus Options

– Supports 3 Input Color Bit-Depth Options:

– RGB888, YCrCb888

– RGB666, YCrCb666

– RGB565, 4:2:2 YCrCb

Pixel Data Processing:

– Image Resizing (Scaling)

– Frame Rate Conversion

– Color Coordinate Adjustment

– Automatic Gain Control

– Programmable Degamma

– Spatial-Temporal Multiplexing (Dithering)

– Video Processing Support:

– Color Space Conversion

– 4:2:2 to 4:4:4 Chroma Interpolation

– Field Scaled De-Interlacing

Packaged in a 176-Pin, 0.4-mm Pitch, VFBGA

External Memory Support:

– 166-MHz Mobile DDR SDRAM

– 33.3-MHz Serial Flash

WVGA, VGA, and nHD DMD Display Support

– DMD Bit-Plane Generation and Formatting

– Programmable Bit-Plane Display Sequencer

(Controls the LED Enables and DMD Loading)

– 76.2-MHz Double Data Rate (DDR) DMD I/F

– Pulse-Width Modulation (PWM) for Mirrors:

– Auto DMD Parking at Power-Down

– 24-Bit Bit-Depth on DMD

System Control:

– I2C Control of Device Configuration

– Programmable Splash Screens

– Programmable LED Current Control

– DMD Power and Mirror Driver Control

– DMD Horizontal and Vertical Display Image

+

•

1

Flip

– Display Image Rotation

– Flash-Based Configuration Batch Files

– I/F Sleep Still Image Power Savings Mode

Test Support:

– Built-In Test Pattern Generation

– JTAG With Boundary Scan Test Support

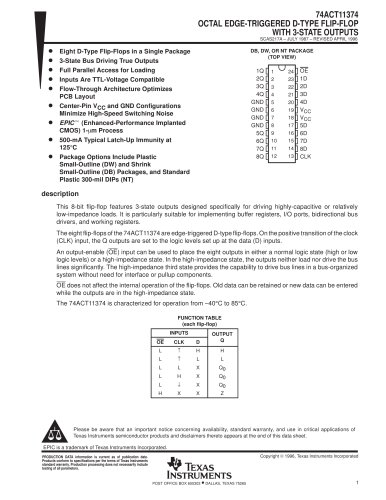

L5

DC

Supplies

2.3V-5.5V

Connector

PWR_EN

Dual

Reg.

SYSPWR

PROJ_ON

1.8V

1.0V

L6

VLED

RESETZ

PARKZ

PROJ_ON

Application

Processor

CLRL

4

GPIO4

SPI(4)

PAD1000

Analog

ASIC

RED

GREEN

BLUE

LED_SEL(2)

Parallel or

BT.656

DLPC2607

28

24/16/8

L2

Flash

INIT_DONE

L1

INTZ

BIAS, RST, OFS

3

PWM_IN

RGB

Illumination

Optics

CMP_OUT

DATA

Thermistor

I2C

1.8V

1.0V

DDR

VIO

VCORE

CTRL

DATA

nHD/WVGA

WVGA

DDR DMD

GPIO5

DDR

Mobile SDRAM

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید