CP2108 Single-Chip USB-to-Quad-UART Bridge0 pages

CP2108

S INGLE - C HIP USB- T O - Q U A D - U A R T B R ID G E

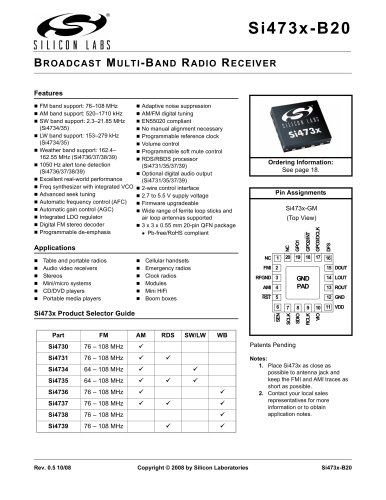

Single-Chip USB-to-QUAD UART Data Transfer

UART Interface Features

Four

independent UART interfaces

Integrated USB transceiver; no external resistor

required

Integrated clock; no external crystal required

Integrated programmable EEPROM for storing

customizable product information

On-chip power-on reset circuit

On-chip voltage regulator: 3.3 V output

Each UART interface supports the following:

Supports hardware flow control (RTS/CTS)

Supports all modem control signals

Data formats supported:

- Data bits: 5, 6, 7, and 8

- Stop bits: 1, 1.5, and 2

- Parity: odd, even, set, mark and none

Baud rates: 300 bps to 2 Mbps

UART 3 (pins 1–6) supports interfacing to devices up to

6V

USB Peripheral Function Controller

USB

USB

Specification 2.0 compliant; full-speed (12 Mbps)

suspend states supported via SUSPEND pins

GPIO Interface Features

Total

of 16 GPIO pins with configurable options

pin support

Usable as inputs, open-drain or push-pull outputs

4 configurable clock outputs for external devices

RS-485 bus transceiver control

Toggle LED upon transmission

Toggle LED upon reception

Virtual COM Port Drivers

Suspend

Works

with existing COM port PC applications

distribution license

Windows 8/7/Vista/XP/Server 2003

Mac OS X

Linux

Royalty-free

Package Options

Supply Voltage

RoHS-UART

Self-powered:

3.0 to 3.6 V

USB bus powered: 4.0 to 5.5 V

VIO voltage: 3.0 to VDD

VIOHD

3 compliant 64-pin QFN (9x9 mm)

Temperature Range

–40

voltage: 2.7 to 6 V

to +85 °C

Ordering Part Number

CP2108-B02-GM

CP2108

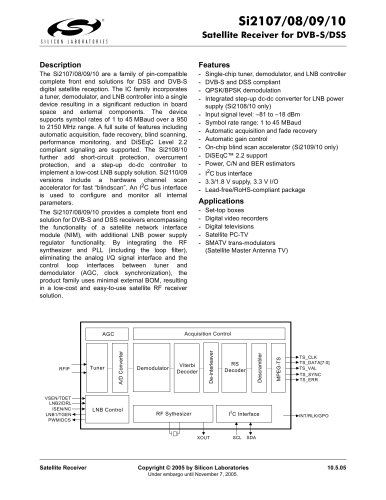

Connect to VBUS

or External Supply

VREGIN

VDD

Voltage

Regulator

80 MHz

Oscillator

Baud Rate

Generator

RI(0-3)

Clock Divider

DCD(0-3)

UART0

DTR(0-3)

VSS

USB Interface

USB

Connector

VBUS

D+

D-

Handshake Control

VBUS

D+

D-

Full-Speed

12 Mbps

Transceiver

Peripheral

Function

Controller

Data

FIFO

6

DSR(0-3)

RTS(0-3)

UART1

CTS(0-3)

UARTn (0-3)

VIO

GND

RX(0-3)

TX(0-3)

UART2

GPIO.0 – GPIO.15

18

EEPROM

(Product Customization)

SUSPEND

UART3

/SUSPEND

RESET

(3.0 V to VDD)

(2.7 to 6.0 V)

VIO

I/O Power and Logic Levels UART0-2, GPIO, SUSPEND, RESET

VIOHD

High Drive UART 3(Pins 1-6)

Figure 1. Example System Diagram

Rev. 1.1 2/14

Copyright © 2014 by Silicon Laboratories

CP2108

"

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید