Eden® X2 (Dual Core)0 pages

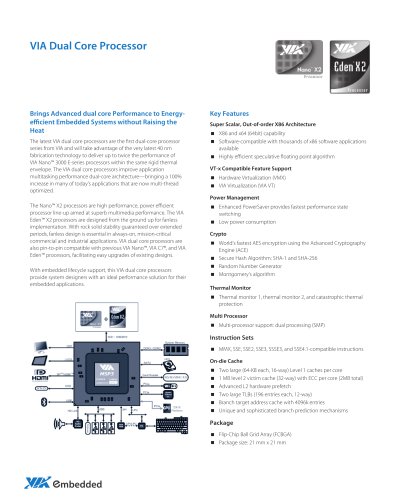

VIA Dual Core Processor

Brings Advanced dual core Performance to Energyefficient Embedded Systems without Raising the

Heat

The latest VIA dual core processors are the first dual-core processor

series from VIA and will take advantage of the very latest 40 nm

fabrication technology to deliver up to twice the performance of

VIA Nano™ 3000 E-series processors within the same rigid thermal

envelope. The VIA dual core processors improve application

multitasking performance dual-core architecture—bringing a 100%

increase in many of today's applications that are now multi-thread

optimized.

Key Features

Super Scalar, Out-of-order X86 Architecture

X86 and x64 (64bit) capability

Software-compatible with thousands of x86 software applications

available

Highly efficient speculative floating point algorithm

VT-x Compatible Feature Support

Hardware Virtualization (VMX)

VIA Virtualization (VIA VT)

Power Management

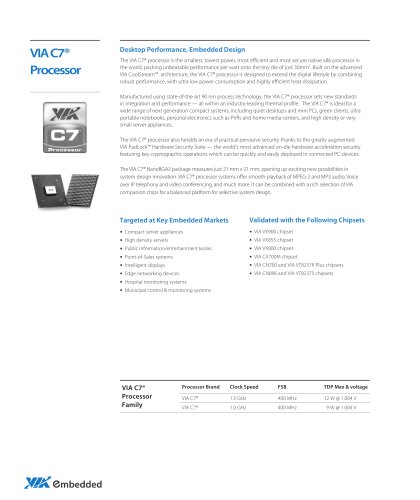

The Nano™ X2 processors are high performance, power efficient

processor line-up aimed at superb multimedia performance. The VIA

Eden™ X2 processors are designed from the ground up for fanless

implementation. With rock solid stability guaranteed over extended

periods, fanless design is essential in always-on, mission-critical

commercial and industrial applications. VIA dual core processors are

also pin-to-pin compatible with previous VIA Nano™, VIA C7®, and VIA

Eden™ processors, facilitating easy upgrades of existing designs.

With embedded lifecycle support, this VIA dual core processors

provide system designers with an ideal performance solution for their

embedded applications.

Enhanced PowerSaver provides fastest performance state

switching

Low power consumption

Crypto

World’s fastest AES encryption using the Advanced Cryptography

Engine (ACE)

Secure Hash Algorithm: SHA-1 and SHA-256

Random Number Generator

Montgomery’s algorithm

Thermal Monitor

Thermal monitor 1, thermal monitor 2, and catastrophic thermal

protection

Multi Processor

Multi-processor support: dual processing (SMP)

Instruction Sets

MMX, SSE, SSE2, SSE3, SSSE3, and SSE4.1-compatible instructions

On-die Cache

Two large (64-KB each, 16-way) Level 1 caches per core

1 MB level 2 victim cache (32-way) with ECC per core (2MB total)

Advanced L2 hardware prefetch

Two large TLBs (196 entries each, 12-way)

Branch target address cache with 4096k entries

Unique and sophisticated branch prediction mechanisms

Package

Flip-Chip Ball Grid Array (FCBGA)

Package size: 21 mm x 21 mm

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید