DS3922 High-Speed Current Mirror and Integrated FETs for DC-DC Controller0 pages

DS3922

High-Speed Current Mirror and

Integrated FETs for DC-DC Controller

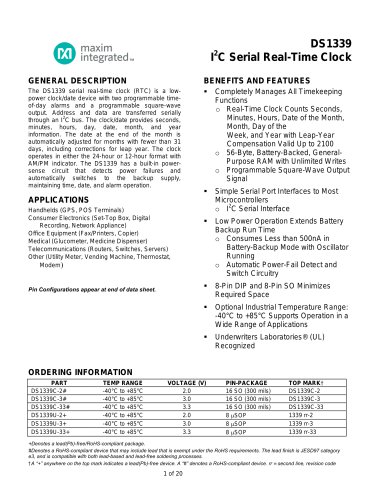

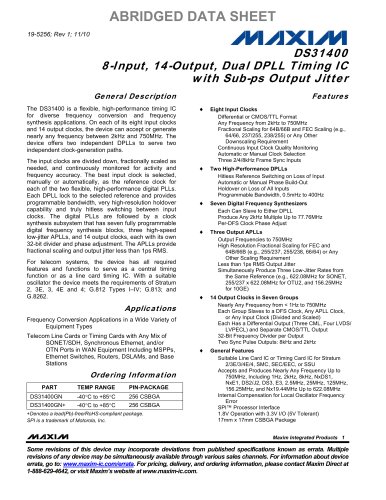

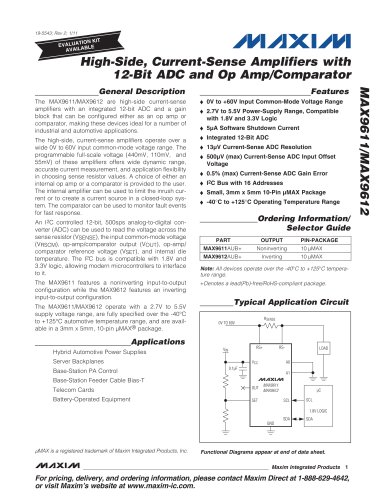

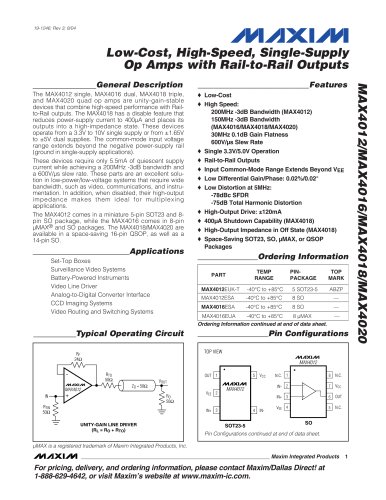

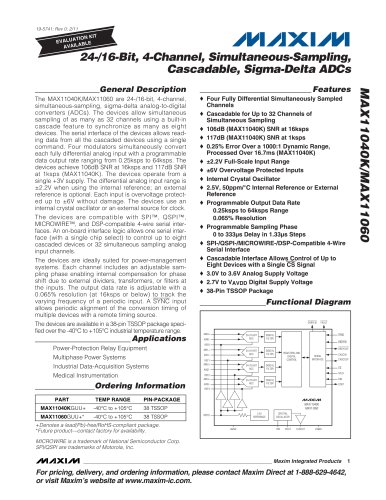

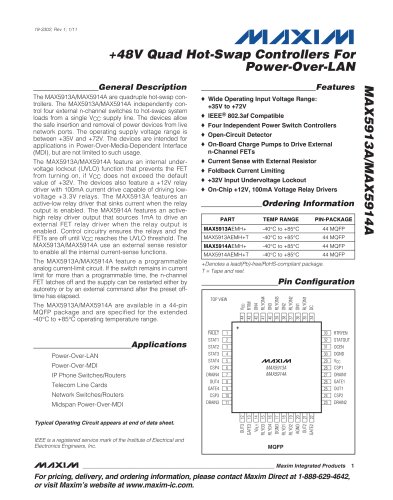

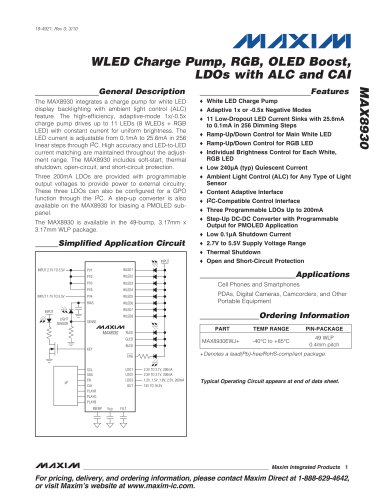

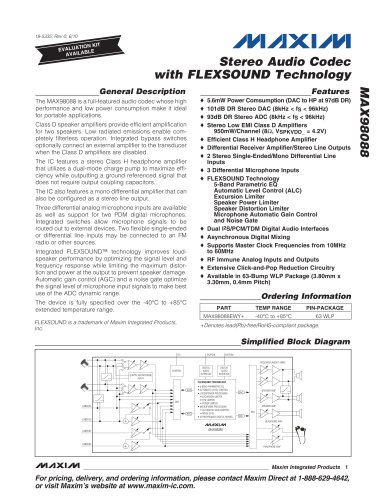

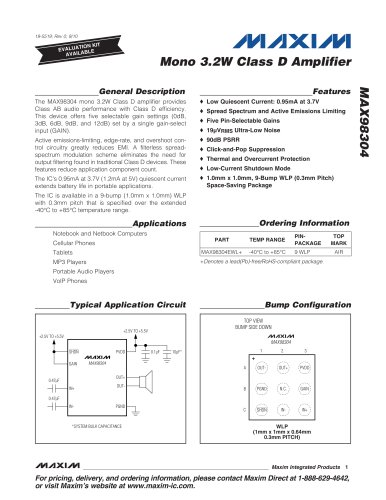

General Description

The DS3922 high-speed current mirror integrates highvoltage devices necessary for monitoring the burst mode

receive power signal in avalanche photodiode (APD) biasing and OLT applications. The device has two small and

one large gain current mirror outputs to monitor the APD

current. An adjustable current clamp limits current through

the APD. The clamp also features an external shutdown.

An integrated FET is also provided that can be used with

an external DC-DC controller to create a high-voltage

boost DC-DC converter. Integrated low-voltage FET

circuits can be used to create buck, boost, and inverting

DC-DC converters for efficient laser bias and EML bias

applications.

The DS3922 is available in a 24-pin TQFN package and

operates over an extended -40°C to +95°C temperature

range.

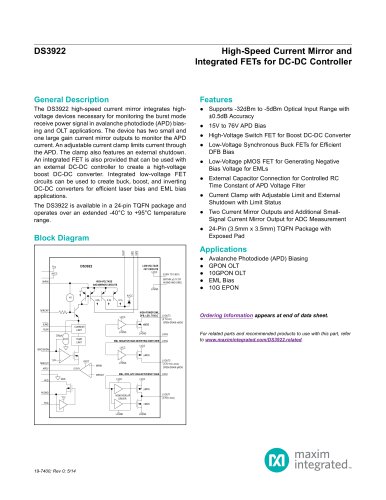

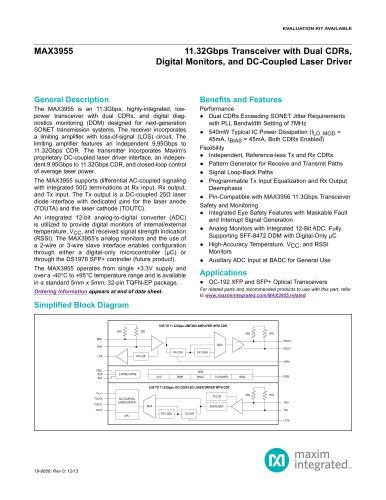

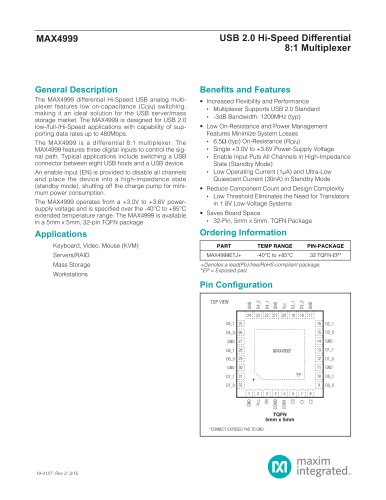

VIP2

IOUT

VIP1

AVCC

LVGND

I1

0.8I1

0.2I1

LVCC

200µA

TEMP

LIMIT

HIGH-POWER DML,

DFB, LDD, TXVCC

LVGND

CURRENT

LIMIT

LVGND

LVOUT3

(0 TO 4V)

OPEN-DRAIN nMOS

LVIN3

EML NEGATIVE BIAS INVERTING SWITCHER LVIN2

LVCC

ISRC/SHDN

LVCC

pMOS

1.8V

AVCC

0.5V/V

APDV

MIRIN

MIROUT

HVD

●t Low-Voltage Synchronous Buck FETs for Efficient

DFB Bias

●t Low-Voltage pMOS FET for Generating Negative

Bias Voltage for EMLs

●t External Capacitor Connection for Controlled RC

Time Constant of APD Voltage Filter

●t Current Clamp with Adjustable Limit and External

Shutdown with Limit Status

●t Two Current Mirror Outputs and Additional SmallSignal Current Mirror Output for ADC Measurement

●t

●t

●t

●t

●t

Avalanche Photodiode (APD) Biasing

GPON OLT

10GPON OLT

EML Bias

10G EPON

0.1I1

MIRCAP

MIROUT

●t High-Voltage Switch FET for Boost DC-DC Converter

AVCC

4V

RLIM

(2.85V TO 3.63V)

(WITHIN ±0.1V OF

HVGND AND GND)

HIGH-VOLTAGE

AND MIRROR CIRCUITS

ILIMS

●t 15V to 76V APD Bias

Applications

LOW-VOLTAGE

FET CIRCUITS

LVCC

DS3922

MIRIN

●t Supports -32dBm to -5dBm Optical Input Range with

±0.5dB Accuracy

●t 24-Pin (3.5mm x 3.5mm) TQFN Package with

Exposed Pad

Block Diagram

VCC

Features

GND

LVOUT2

(-3.7V TO LVCC)

OPEN-DRAIN pMOS

LVGND

EML, DFB, APC HIGH-EFFICIENCY BIAS LVIN1

LVCC

LVCC

pMOS

HVGND

VCC

HVG

nMOS

LVGND

19-7400; Rev 0; 5/14

LVOUT1

(0 TO LVCC)

NONOVERLAP

DRIVER

LVGND

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer

to www.maximintegrated.com/DS3922.related.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید