ADF4155: Integer-N/Fractional-N PLL Synthesizer0 pages

Integer-N/Fractional-N PLL Synthesizer

ADF4155

Data Sheet

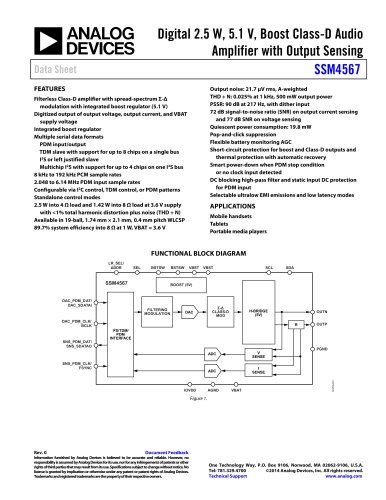

FEATURES

GENERAL DESCRIPTION

Input frequency range: 500 MHz to 8000 MHz

Fractional-N synthesizer and integer-N synthesizer

Phase frequency detector (PFD) up to 125 MHz

High resolution 38-bit modulus

Separate charge pump supply (VP) allows extended tuning

voltage in 5 V systems

Programmable divide by 1, 2, 4, 8, 16, 32, or 64 output

Differential and single-ended reference inputs

Power supply: 3.3 V ± 5%

Logic compatibility: 1.8 V

Programmable dual-modulus prescaler (P) of 4/5 or 8/9

Programmable output power level

3-wire serial interface

Analog and digital lock detect

The ADF4155 allows implementation of fractional-N or

integer-N phase-locked loop (PLL) frequency synthesizers

when used with an external loop filter, external voltage

controlled oscillator (VCO), and external reference frequency.

The ADF4155 is for use with external VCO parts up to an

8 GHz operating frequency. The high resolution programmable

modulus allows synthesis of exact frequencies with 0 Hz error.

The VCO frequency can be divided by 1, 2, 4, 8, 16, 32, or 64 to

allow the user to generate RF output frequencies as low as

7.8125 MHz.

Control of all on-chip registers is through a simple 3-wire

interface. The device operates with a nominal power supply of

3.3 V ± 5% and can be powered down when not in use.

APPLICATIONS

The ADF4155 is available in a 24-lead, 4 mm × 4 mm LFCSP

package.

Wireless infrastructure (W-CDMA, TD-SCDMA, WiMAX, GSM,

PCS, DCS, DECT)

Point to point/point to multipoint microwave links

Test equipment

Wireless LANs, CATV equipment

Clock generation

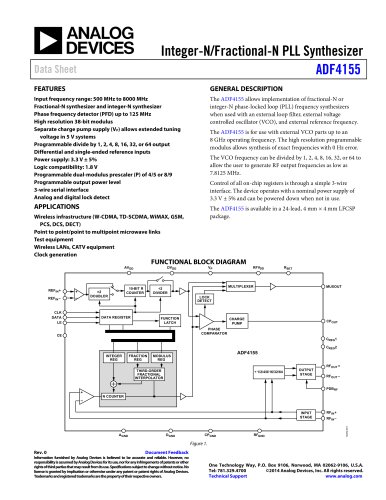

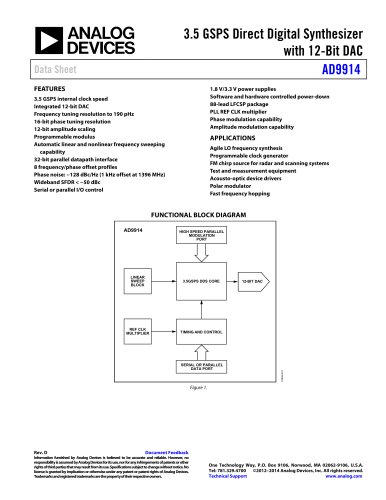

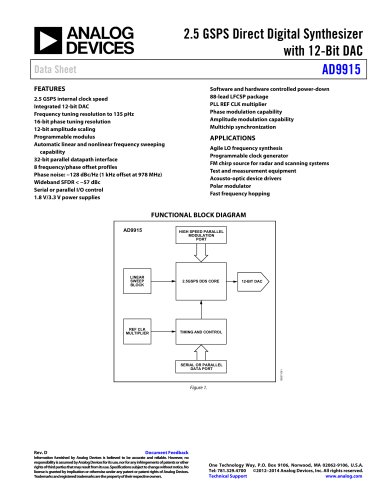

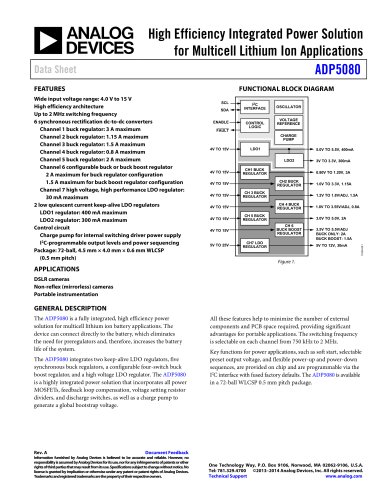

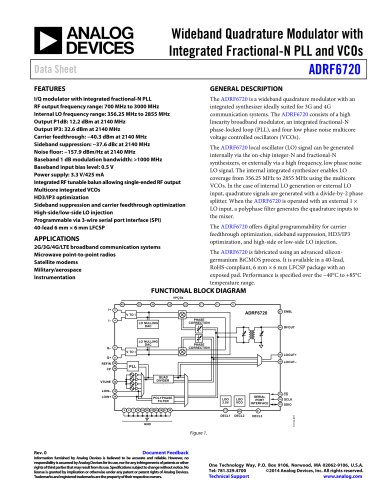

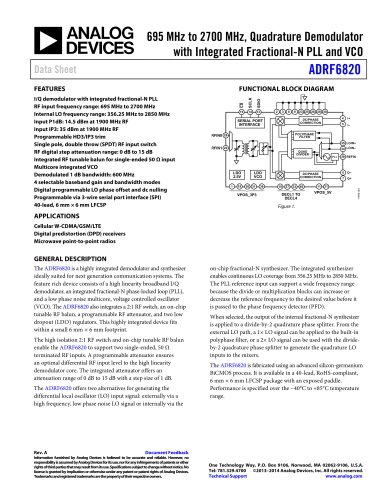

FUNCTIONAL BLOCK DIAGRAM

AVDD

REFIN +

REFIN –

CLK

DATA

LE

DVDD

10-BIT R

COUNTER

×2

DOUBLER

RFVDD

VP

RSET

MULTIPLEXER

÷2

DIVIDER

MUXOUT

LOCK

DETECT

DATA REGISTER

FUNCTION

LATCH

CHARGE

PUMP

CPOUT

PHASE

COMPARATOR

CE

CREG1

CREG2

INTEGER

REG

FRACTION

REG

ADF4155

MODULUS

REG

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

÷ 1/2/4/8/16/32/64

OUTPUT

STAGE

RFOUT +

RFOUT –

PDBRF

N COUNTER

AGND

DGND

CPGND

RFGND

RFIN +

RFIN –

12262-001

INPUT

STAGE

Figure 1.

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2014 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید