Quad Analog Switch/Quad Multiplexer 0 pages

© Semiconductor Components Industries, LLC, 2009

September, 2009 - Rev. 8

1 Publication Order Number:

MC14016B/D

MC14016B

Quad Analog Switch/

Quad Multiplexer

The MC14016B quad bilateral switch is constructed with MOS

P-channel and N-channel enhancement mode devices in a single

monolithic structure. Each MC14016B consists of four independent

switches capable of controlling either digital or analog signals. The

quad bilateral switch is used in signal gating, chopper, modulator,

demodulator and CMOS logic implementation.

Features

• Diode Protection on All Inputs

• Supply Voltage Range = 3.0 Vdc to 18 Vdc

• Linearized Transfer Characteristics

• Low Noise - 12 nV/ãCycle, f 1.0 kHz typical

• Pin-for-Pin Replacements for CD4016B, CD4066B (Note improved

transfer characteristic design causes more parasitic coupling

capacitance than CD4016)

• For Lower RON, Use The HC4016 High-Speed CMOS Device or

The MC14066B

• This Device Has Inputs and Outputs Which Do Not Have ESD

Protection. Antistatic Precautions Must Be Taken.

• These are Pb-Free Devices

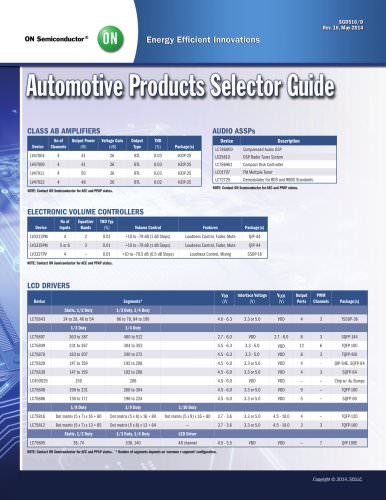

MAXIMUM RATINGS (Voltages Referenced to VSS)

Symbol Parameter Value Unit

VDD DC Supply Voltage Range -0.5 to +18.0 V

Vin, Vout Input or Output Voltage Range

(DC or Transient)

-0.5 to VDD + 0.5 V

Iin Input Current (DC or Transient)

per Control Pin

±10 mA

ISW Switch Through Current ±25 mA

PD Power Dissipation, per Package

(Note 1)

500 mW

TA Ambient Temperature Range -55 to +125 °C

Tstg Storage Temperature Range -65 to +150 °C

TL Lead Temperature

(8-Second Soldering)

260 °C

Stresses exceeding Maximum Ratings may damage the device. Maximum

Ratings are stress ratings only. Functional operation above the Recommended

Operating Conditions is not implied. Extended exposure to stresses above the

Recommended Operating Conditions may affect device reliability.

1. Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/C From 65C To 125C

This device contains protection circuitry to guard against damage due to high

static voltages or electric fields. However, precautions must be taken to avoid

applications of any voltage higher than maximum rated voltages to this

high-impedance circuit. For proper operation, Vin and Vout should be constrained

to the range VSS (Vin or Vout) VDD.

Unused inputs must always be tied to an appropriate logic voltage level

(e.g., either VSS or VDD). Unused outputs must be left open.

http://onsemi.com

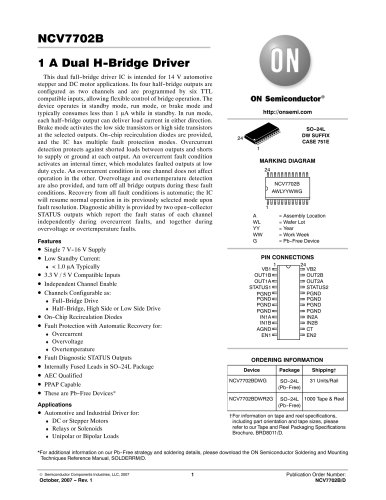

MARKING

DIAGRAMS

1

14

PDIP-14

P SUFFIX

CASE 646

MC14016BCP

AWLYYWWG

SOIC-14

D SUFFIX

CASE 751A

1

14

14016BG

AWLYWW

A = Assembly Location

WL, L = Wafer Lot

YY, Y = Year

WW, W = Work Week

G = Pb-Free Indicator

SOEIAJ-14

F SUFFIX

CASE 965

1

14

MC14016B

ALYWG

See detailed ordering and shipping information in the package

dimensions section on page 2 of this data sheet.

ORDERING INFORMATION

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید