D-MOT-10 FPGA IP Core0 pages

&m RIFTEK

S\ Sensors & Instruments

We implement ideas

Video Tracking and Image Processing Cores

D-MOT-10 FPGA IP CORE FOR MOTION

DETECTION IN VIDEO STREAM IMAGES FPGA

The D-MOT-10 FPGA IP core for motion detection in

video stream images is a completed module intended to be

used in vision systems for various applications (security sys-

tems, specialized systems, etc.) that are based on FPGA.

The core represents a simple data exchange interface that

ensures easy integration into various systems. The algo-

rithms are perfectly suitable for motion detection of ground,

surface and aerial objects of any type.

The implemented algorithms provide detecting of

small-size and low-contrast objects against a complex back-

ground. When an object is detected the core assigns it a

unique number and determinates the movement direction.

This makes it easy to track the object behavior and build

efficient analytical system (perimeter defense, road traffic

control and etc.) When a moving object is detected its mo-

tion path is calculated. In case the object disappears from

the field of vision (for instance, behind an obstacle) the core

predicts the path and detects the object when it re-appears.

It is possible to detect up to 128 moving objects simultane-

ously. Thus, the D-MOT-10 IP core is a completed module

that allows its use in any FPGA projects for vision systems.

BASIC CHARACTERISTICS

Max number of moving objects detecting simultaneously is

up to 128.

Max size of detecting object is limited by the size of pro-

cessed area.

Min size of detecting object is 8x8 pixels size in an image

area.

Max speed of the object for its stable detection is no more

than 30 pixels per frame. Min speed no less than 0A_ pixels

per frame in any direction.

Stable detection of moving objects with contrast from 10%.

Max frame size is up to 720x576 pixels. When it is needed

to process big images it is recommended to use several

cores simultaneously.

Output coordinates are obtained with ± pixel accuracy.

Output coordinates delay is 1 frame.

Processing of grayscale images with the bitness of 8 bits/

pixel.

Output information on the detected objects is detecting

strobe position, its unique number and motion direction.

INTERACTION INTERFACE

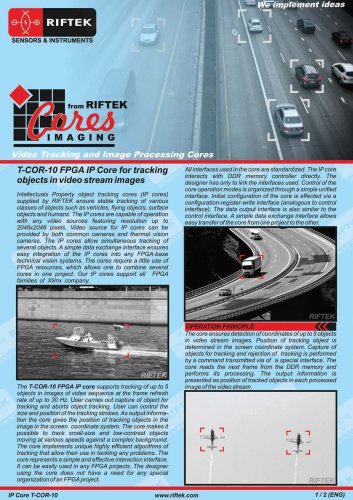

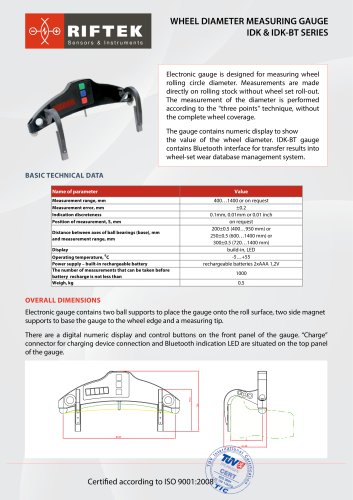

The figure shows the interaction of the IP core with

FPGA project.

SvsClk — Clock signal for the core. All signals for the core

must be synchronized with Sys Clk.

Rst — Core reset signal.

Conflnr7:0l ConflnA, ConflnAp — Interface for writing

configuration registers.

NF— New frame signal.

UpdFilters — The core filters reset signal.

SysClk

Rst

>

Confln[7:0] I

ConflnA ->

ConflnAp ->

NF ->

UpdFilters-*>

FBI [2:0] f_

DDR Controller

DDR interface

TrgtsDataA

TrgtsDataAp

TrgtsData [135:0] ^~

yr

mn

IMAGING

CORE:

Motion Detector

D-MOT-10

FBI12:0]— Bus for the current frame buffer index.

DDR interface — Unified interface for data exchange with

the DDRXilinx®.

IP Core D-MOT-10

www.riftek. com

1/2 (ENG)

"

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید