Application JTAG/Boundary Scan0 pages

JTAG/Boundary Scan

JTAG/Boundary Scan

Applications Based on Embedded System Access (ESA)

Classication of Target Applications

Laboratory

Production test

Structural

functional test

Each application pursues certain basic objectives, such as testing,

programming, debugging or validation, and is dened by certain very specic

characteristics, such as execution speed, execution environment or interaction

with other instruments. In this context, the following application types

are especially important for Embedded System Access (ESA).

Multi-dimensional JTAG/Boundary Scan platform

System interaction

Embedded System Access

Intrusive Board Access

Native Connector Access

•

•

•

•

•

•

• In-Circuit Test

• Manufacturing Defects

Analyser

• Flying Probe Test

• In-Circuit Emulation

• Probe based test and

measurement instruments

•

•

•

•

•

JTAG/Boundary Scan

Processor Emulation Test

Chip-embedded Instruments

Embedded Diagnostics Test

In-System Programming

Core-Assisted Programming

Keeping Track of the Entire Workow

Functional Test

Performance test

Hot mockup test

System bus emulation

Run-in-test monitoring

Application type

Design concept

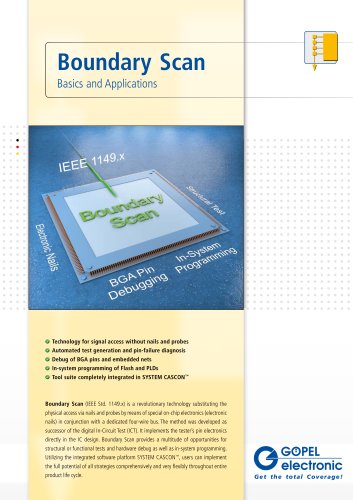

Structural test

Checking the proper connection between the various circuitry elements

Functional test

Execution: structural, functional or emulation test at higher speed

Design verification

(simulation)

Measurement of voltage, frequency, temperature, waveform

Debugging

Automatic

test bench

generation

Physical

prototyping

JTAG/Boundary

Scan chip tester

JTAG/Boundary

Scan board tester

Design verification

(analysis of the

test coverage)

Physical

prototyping

In addition to the core process for testing and programming, successful project

development also requires a number of supplementary processes such as:

• BSDL validation

(BSDL: Boundary Scan Description Language)

• Test program debugging

• Hardware debugging

• Optimisation of testability

• Optimisation of fault coverage

BSDL: connecting element between design and test

Objective

BSDL validation

goepel.com/

goepel.com/en/esa/integration

Application development

for test and programming

Syntax check

Semantics check

Testbench generation for simulations

Physical verication of the BSDL le against

the silicon

•

•

•

•

TAP Checker

Syntax & Semantic Checker

ATPG/PFD Infrastructure

Device Checker Hardware

•

•

•

•

•

•

•

•

•

•

•

Test program debugging

Pin toggling

Scan cell toggling

Data register watching

Data register loading

Waveform analysis

Network analysis

Instructions change

Circuit verication

Fault isolation

Pin status detection

•

•

•

•

•

•

•

ScanAssist Interactive Pin-Toggler

ScanAssist Multi Mode Debugger

ScanVision Schematic

ScanVision Layout

ScanVision Virtual Schematic

Advanced Vector Browser

PicoTAP, SCANBOOSTER or SCANFLEX Controller

•

•

•

•

•

Testability reviews

Optimisation of test coverage

Maximisation of throughput

Denition of the test strategy

Qualication of the integration strategy

•

•

•

•

•

Design and Testability Explorer

Test Coverage Analyser

ScanVision Schematic

ScanVision Layout

ScanVision Virtual Schematic

Debugging

High-speed programming

NAND/NOR ash

Workow including debugging and test optimisation

PLD/FPGA programming

Analog I/O Test

LAN interface test

BGA debugging

Connection test

JTAG

JTAG / Boundary Scan

Gigabit I/O test

*

JTAG scan chain

Mix with Processor Emulation Test

and Chip-embedded Instruments

JTAG connector access

Access to native connectors

(integration with functional testers)

Buffer test

Test coverage

analysis

Test strategy

Invasive bord access technologies

(integration with ICT, MDA and FPT)

Voltage measurement

Frequency measurement

Temperature measurement

Digital I/O test

Automated inspection

(combination with AOI and AXI)

ICT:

ICT:

MDA:

MDA:

FPT:

FPT:

AOI:

AOI:

AXI:

AXI:

In-Circuit Test

Manufacturing Defects Analyser

Flying Probe Tester

Automated Optical Inspection

Automated X-Ray Inspection

Integration

strategy

JTAG/Boundary Scan

Software/hardware

•

•

•

•

Project data

preparation

Test optimisation

Application

For these processes, too, we offer fully integrated support as part of the available hardware

and software platforms, thus ensuring that the entire workow can be covered in a

single system environment.

Programming of non-volatile memory (ash, micro controller, PLD)

Prototype test &

programmierung

and physical

BSDL validation

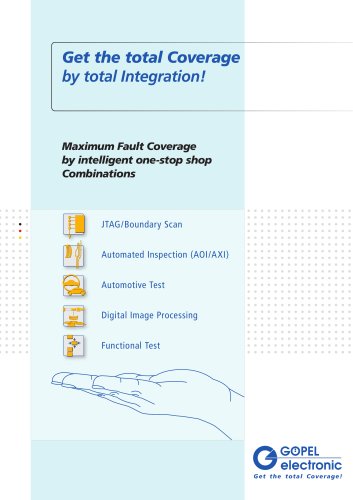

Our multi-dimensional JTAG/Boundary Scan platform supports not only

all of the above mentioned applications, but also offers the option to

interactively combine other access methods through open system integration.

In this way, we are able to provide a exible and universally deployable

solution.

High-speed programming

serial ash (I2C, SPI, …)

BSDL

Syntax

Checker

Interactive test of individual registers, pins, connections or logic functions

Programming

Design concept

Generation

PASS

Execution: structural, functional or emulation test at nominal speed

Analog measurement

Further information on test strategies and

system integration is available at

or

BSDL

file

Test conducted by the micro processor through emulation

(special instance of functional test)

Real time test

Correlation between application, instrumentation and access

BSDL export

from library

Checking the proper functioning of ICs, clusters, boards, interfaces and systems

Emulation test

Manual BSDL

development

Generation

Key application contents

At-speed test

i

Available tools & services by GOEPEL electronic

BSDL

validation

Systems

Sales staff

System

maintenance

Debugging

Boards

Debugging

Design

validation

Test

optimisations

Chips

Production

Component

programming

The Proper Tool for Each Application

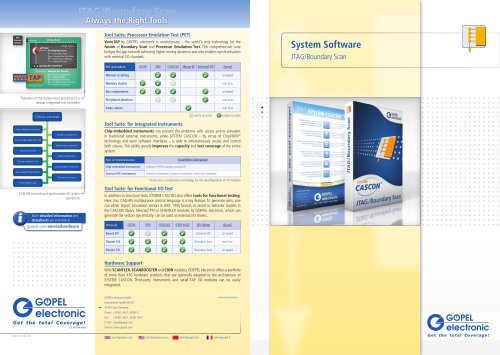

All processes are included in the principle of graphic project development on which

the SYSTEM CASCON is based.

This is made possible by extremely powerful visualisation tools, such as Mission

Assist™ oder ScanVision™, which are fully integrated into the software platform.

In addition, we offer a broad range of ATE integration packages and automated

inspection systems aimed specically at test optimisation.

Inspection

strategy

i

*TestWay is made by ASTER Technologies and is

recommended by GOEPEL electronic for complex

overall analyses of fault coverage

BSDL Verication • Design Validation • Hardware Debugging • Component Programming •

Structural Test • Functional Test • Emulation Test • Mixed Signal Test • Optoelectric Test

Detailed information and datasheets on our products and integration solutions

are available at

goepel.com/

goepel.com/en/esa/instruments

goepel.com/en/esa/integration

Gradual optimisation of fault coverage

GOEPEL electronic GmbH

Button Test

Authorised Distributor:

Goeschwitzer Straße 58 / 60

07745 Jena / Germany

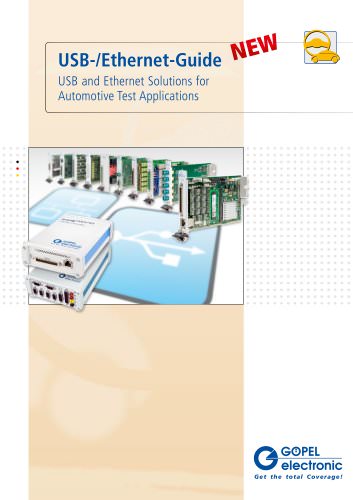

USB interface test

DDR-SDRAM access test

Phone: + 49 (0) - 36 41 - 68 96 - 0

Fax:

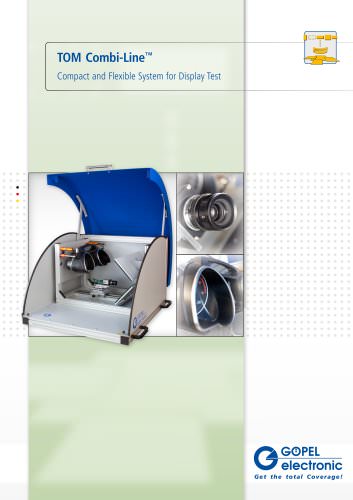

Display test

MCU high-speed programming

ISO 9001 certied

LED test

Practical examples of applications based on Embedded System Access technologies

+ 49 (0) - 36 41 - 68 96 - 944

E-Mail: sales@goepel.com

BST-AF / E / 2012-04

Internet: www.goepel.com

sales@goepel.co.uk

sales@goepelusa.com

sales@goepel.asia

sales@goepel.fr

Get the total Coverage!

"

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید