Calibre xRC0 pages

Fast, Accurate, Rule-Based Parasitic Extraction

Circuit Verification

Calibre xRC

D A T A S H E E T

BENEFITS:

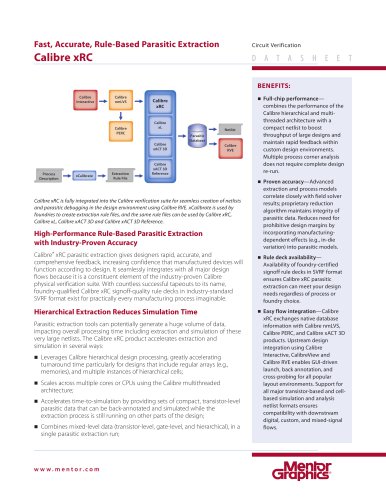

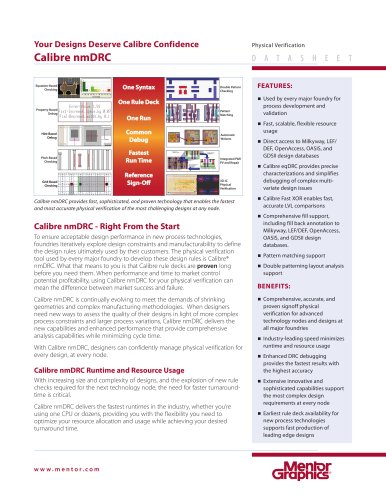

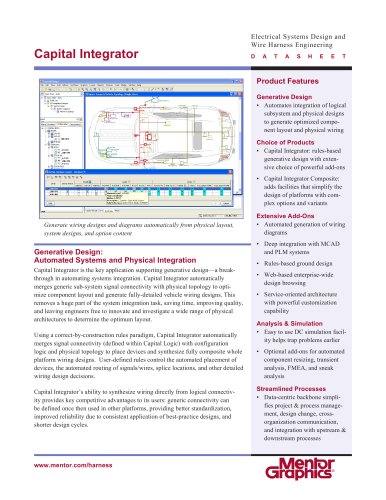

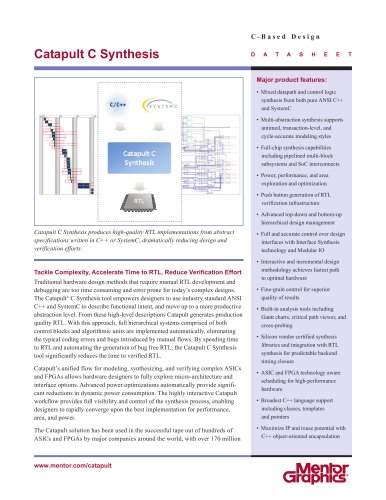

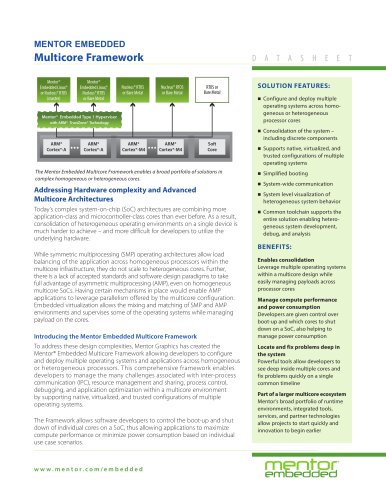

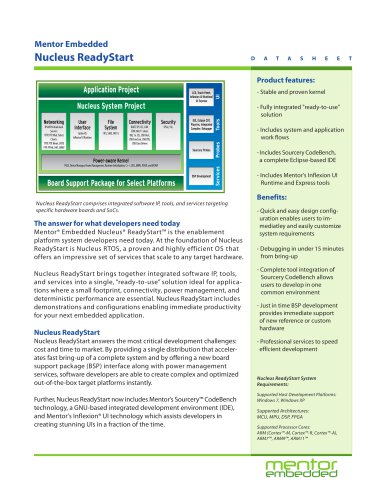

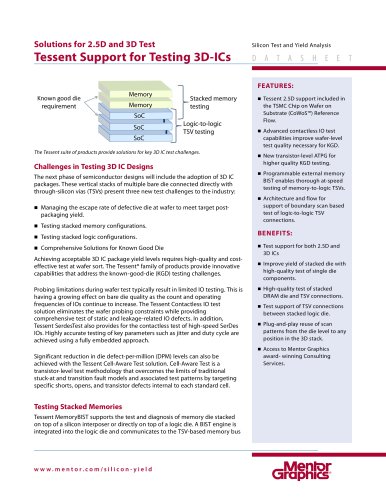

Calibre

Interactive

Calibre

nmLVS

Calibre

PERC

Calibre

xRC

Calibre

xL

Calibre

xACT 3D

Process

Description

xCalibrate

Extraction

Rule File

Netlist

Parasitic

Database

Calibre

RVE

Calibre

xACT 3D

Reference

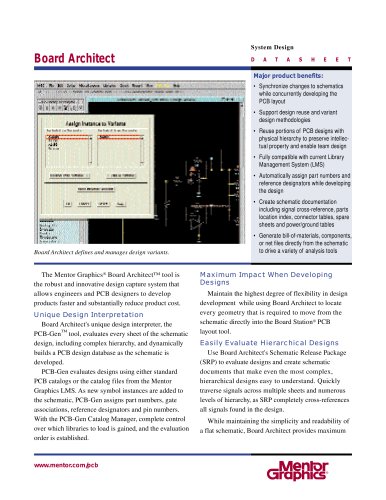

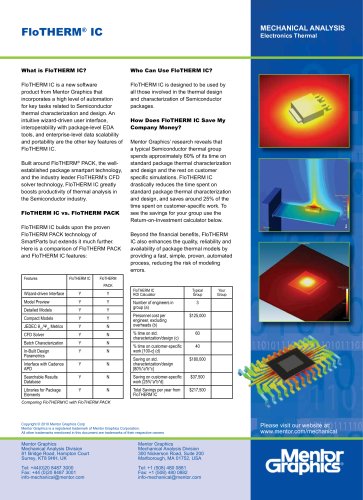

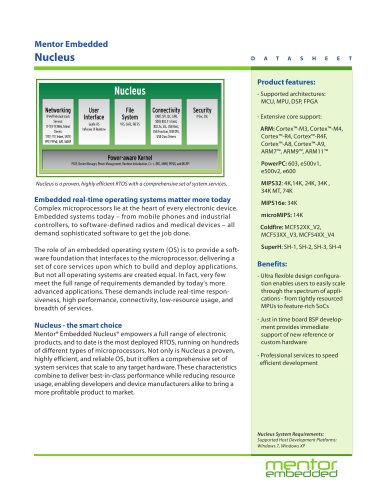

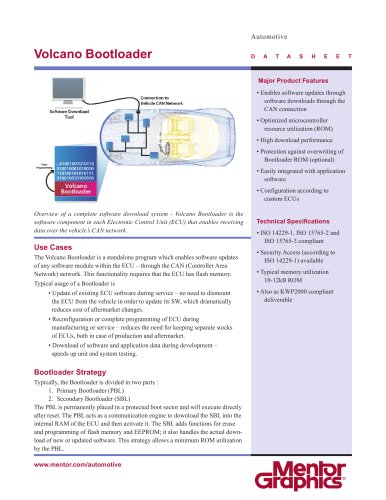

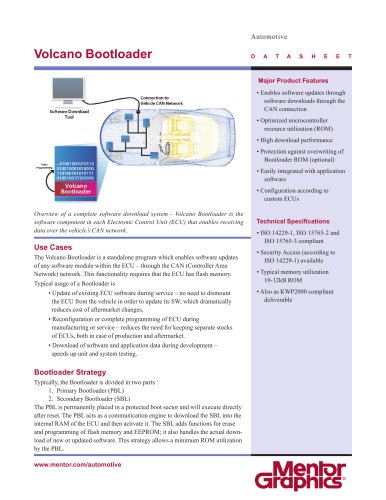

Calibre xRC is fully integrated into the Calibre verification suite for seamless creation of netlists

and parasitic debugging in the design environment using Calibre RVE. xCalibrate is used by

foundries to create extraction rule files, and the same rule files can be used by Calibre xRC,

Calibre xL, Calibre xACT 3D and Calibre xACT 3D Reference.

High-Performance Rule-Based Parasitic Extraction

with Industry-Proven Accuracy

Calibre® xRC parasitic extraction gives designers rapid, accurate, and

comprehensive feedback, increasing confidence that manufactured devices will

function according to design. It seamlessly integrates with all major design

flows because it is a constituent element of the industry-proven Calibre

physical verification suite. With countless successful tapeouts to its name,

foundry-qualified Calibre xRC signoff-quality rule decks in industry-standard

SVRF format exist for practically every manufacturing process imaginable.

Hierarchical Extraction Reduces Simulation Time

Parasitic extraction tools can potentially generate a huge volume of data,

impacting overall processing time including extraction and simulation of these

very large netlists. The Calibre xRC product accelerates extraction and

simulation in several ways:

■■ Leverages Calibre hierarchical design processing, greatly accelerating

turnaround time particularly for designs that include regular arrays (e.g.,

memories), and multiple instances of hierarchical cells;

■■ Scales across multiple cores or CPUs using the Calibre multithreaded

architecture;

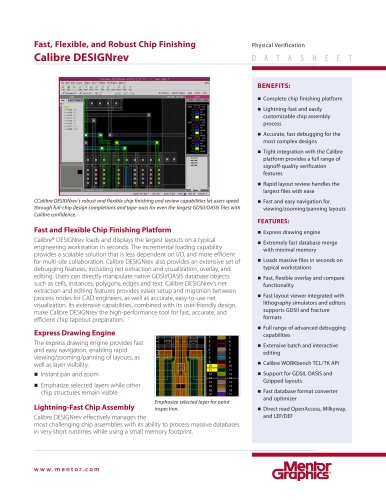

■■ Accelerates time-to-simulation by providing sets of compact, transistor-level

parasitic data that can be back-annotated and simulated while the

extraction process is still running on other parts of the design;

■■ Combines mixed-level data (transistor-level, gate-level, and hierarchical), in a

single parasitic extraction run;

w w w. m e nto r. co m

■■ Full-chip performance—

combines the performance of the

Calibre hierarchical and multithreaded architecture with a

compact netlist to boost

throughput of large designs and

maintain rapid feedback within

custom design environments.

Multiple process corner analysis

does not require complete design

re-run.

■■ Proven accuracy—Advanced

extraction and process models

correlate closely with field solver

results; proprietary reduction

algorithm maintains integrity of

parasitic data. Reduces need for

prohibitive design margins by

incorporating manufacturingdependent effects (e.g., in-die

variation) into parasitic models.

■■ Rule deck availability—

Availability of foundry-certified

signoff rule decks in SVRF format

ensures Calibre xRC parasitic

extraction can meet your design

needs regardless of process or

foundry choice.

■■ Easy flow integration—Calibre

xRC exchanges native database

information with Calibre nmLVS,

Calibre PERC, and Calibre xACT 3D

products. Upstream design

integration using Calibre

Interactive, CalibreView and

Calibre RVE enables GUI-driven

launch, back annotation, and

cross-probing for all popular

layout environments. Support for

all major transistor-based and cellbased simulation and analysis

netlist formats ensures

compatibility with downstream

digital, custom, and mixed-signal

flows.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید