Olympus-SoC0 pages

Place and Route

DATASHEET

www.mentor.com

Benefits

• Boost IC performance with advanced multi-corner, multi-mode optimization

• Improve yield with DFM-aware routing to address lithography issues in a timing context during implementation

• Speed time-to-market with fewer design iterations, scalable multi-threading, and sign-off quality closure

• Reduce costs through high yields and fast time-to-market

Major Product Features

• Patented MCMM optimization during all design steps

• Fast routing with full 65 nm and 45 nm rule support

• Sign-off quality timing analysis and optimization

• Extremely fast and accurate, on-the-fly parasitic extraction

• Floorplanning, rapid design feasibility and constraint

debugging

• Best-in-class, CTS-aware standard cell and macro placement

• Industry’s first MCMM CTS for robust, low-power clock trees

• MCMM SI to concurrently compute delay shift and glitch for any number of mode/corner scenarios in a single pass

• Advanced physical synthesis with built-in OCV and CPPR

• Handles multi-million gate designs hierarchical or flat with faster runtimes

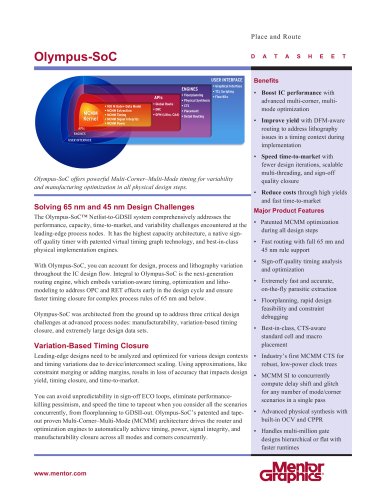

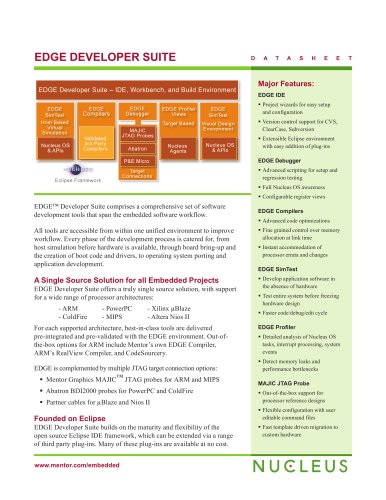

Olympus-SoC

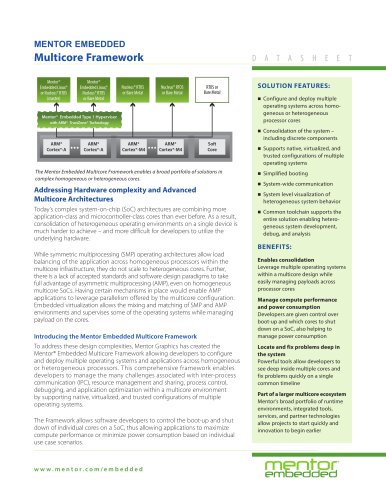

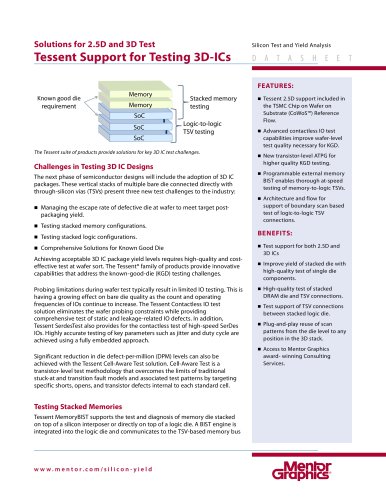

Olympus-SoC offers powerful Multi-Corner–Multi-Mode timing for variability

and manufacturing optimization in all physical design steps.

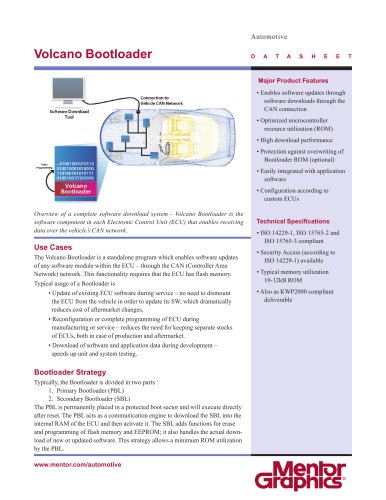

Solving 65 nm and 45 nm Design Challenges

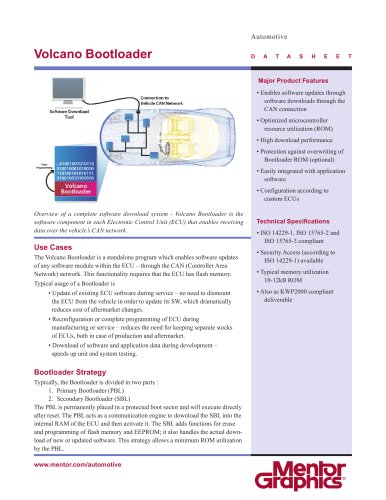

The Olympus-SoC™ Netlist-to-GDSII system comprehensively addresses the performance, capacity, time-to-market, and variability challenges encountered at the leading-edge process nodes. It has the highest capacity architecture, a native sign-off quality timer with patented virtual timing graph technology, and best-in-class physical implementation engines.

With Olympus-SoC, you can account for design, process and lithography variation throughout the IC design flow. Integral to Olympus-SoC is the next-generation routing engine, which embeds variation-aware timing, optimization and litho-modeling to address OPC and RET effects early in the design cycle and ensure faster timing closure for complex process rules of 65 nm and below.

Olympus-SoC was architected from the ground up to address three critical design challenges at advanced process nodes: manufacturability, variation-based timing closure, and extremely large design data sets.

Variation-Based Timing Closure

Leading-edge designs need to be analyzed and optimized for various design contexts and timing variations due to device/interconnect scaling. Using approximations, like constraint merging or adding margins, results in loss of accuracy that impacts design yield, timing closure, and time-to-market.

You can avoid unpredictability in sign-off ECO loops, eliminate performance-killing pessimism, and speed the time to tapeout when you consider all the scenarios concurrently, from floorplanning to GDSII-out. Olympus-SoC’s patented and tape-out proven Multi-Corner–Multi-Mode (MCMM) architecture drives the router and optimization engines to automatically achieve timing, power, signal integrity, and manufacturability closure across all modes and corners concurrently.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید