Vista0 pages

Vista Architect

Electronic System Level Design

System Level Design Solution for Performance and Power

D

A T A

S

H

E

E

T

BENEFITS

Policies

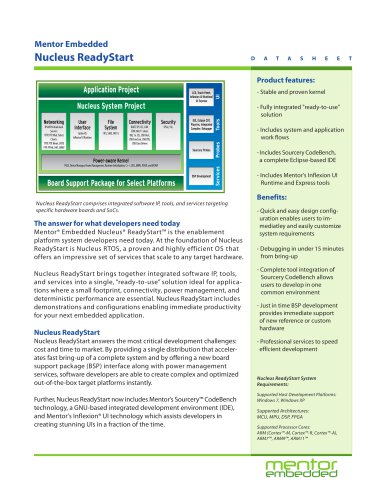

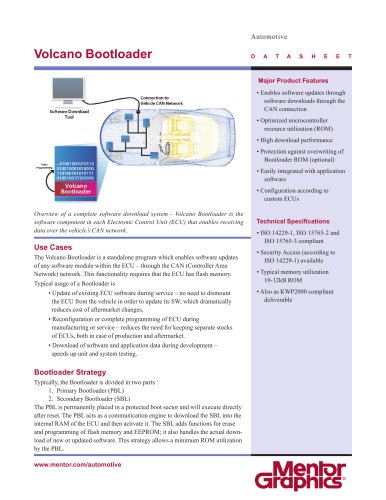

•t Architecture design and

exploration

TLM

TLM

•t Allow hardware / software

tradeoffs analysis

Processor

On Chip Bus

TLM

TLM

TLM

•t Early assessment of performance

and power

TLM

Transaction Level Platform

Model Builder

Virtual Platform

Software

•t Virtual platform for software

integration and validation

Power & Performance

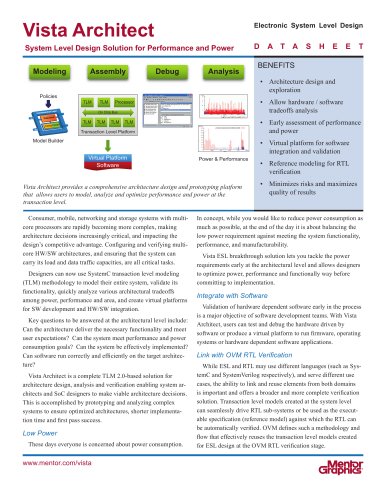

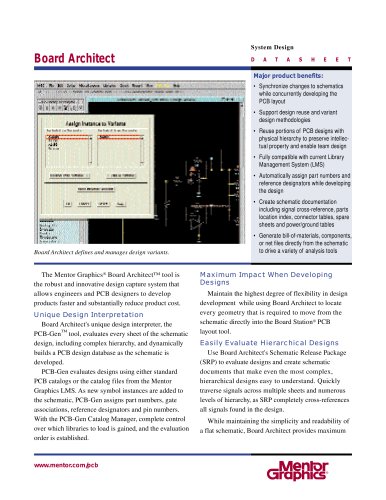

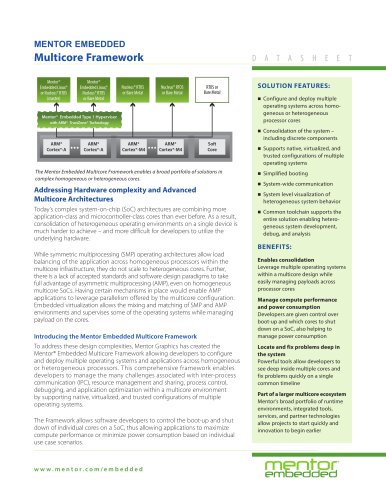

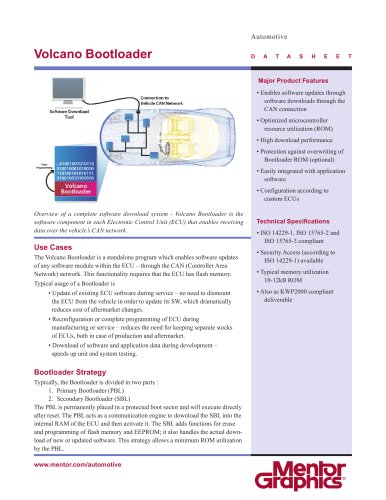

Vista Architect provides a comprehensive architecture design and prototyping platform

that allows users to model, analyze and optimize performance and power at the

transaction level.

Consumer, mobile, networking and storage systems with multicore processors are rapidly becoming more complex, making

architecture decisions increasingly critical, and impacting the

design’s competitive advantage. Configuring and verifying multicore HW/SW architectures, and ensuring that the system can

carry its load and data traffic capacities, are all critical tasks.

Designers can now use SystemC transaction level modeling

(TLM) methodology to model their entire system, validate its

functionality, quickly analyze various architectural tradeoffs

among power, performance and area, and create virtual platforms

for SW development and HW/SW integration.

Key questions to be answered at the architectural level include:

Can the architecture deliver the necessary functionality and meet

user expectations? Can the system meet performance and power

consumption goals? Can the system be effectively implemented?

Can software run correctly and efficiently on the target architecture?

Vista Architect is a complete TLM 2.0-based solution for

architecture design, analysis and verification enabling system architects and SoC designers to make viable architecture decisions.

This is accomplished by prototyping and analyzing complex

systems to ensure optimized architectures, shorter implementation time and first pass success.

Low Power

These days everyone is concerned about power consumption.

www.mentor.com/vista

•t Reference modeling for RTL

verification

•t Minimizes risks and maximizes

quality of results

In concept, while you would like to reduce power consumption as

much as possible, at the end of the day it is about balancing the

low power requirement against meeting the system functionality,

performance, and manufacturability.

Vista ESL breakthrough solution lets you tackle the power

requirements early at the architectural level and allows designers

to optimize power, performance and functionally way before

committing to implementation.

Integrate with Software

Validation of hardware dependent software early in the process

is a major objective of software development teams. With Vista

Architect, users can test and debug the hardware driven by

software or produce a virtual platform to run firmware, operating

systems or hardware dependent software applications.

Link with OVM RTL Verification

While ESL and RTL may use different languages (such as SystemC and SystemVerilog respectively), and serve different use

cases, the ability to link and reuse elements from both domains

is important and offers a broader and more complete verification

solution. Transaction level models created at the system level

can seamlessly drive RTL sub-systems or be used as the executable specification (reference model) against which the RTL can

be automatically verified. OVM defines such a methodology and

flow that effectively reuses the transaction level models created

for ESL design at the OVM RTL verification stage.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید