Calibre OPC and PSM0 pages

Calibre OPC and PSM

Manufacturability

DATASHEET

f - » » I 1 n i I I I ■

«fr — WW OfC WW D—*p OWflg W »m tM I Mft C**» ZMft CM— «ttt W

"□□ancniiicKDEjmGJ"

"++++++++++++"

; I j. -i ■. |l ----.

Omni \ Fn#w»L \ Ltytn \ T*m \

I * ""fr" I

[1£MH

jd.DIH

1 2 | t ■ | t | ■> |

V | |||

• | .. ^ . —■. | ||

.........

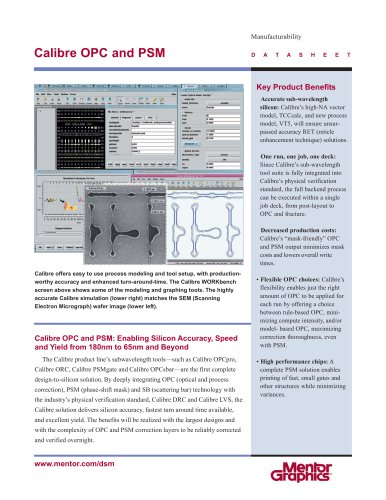

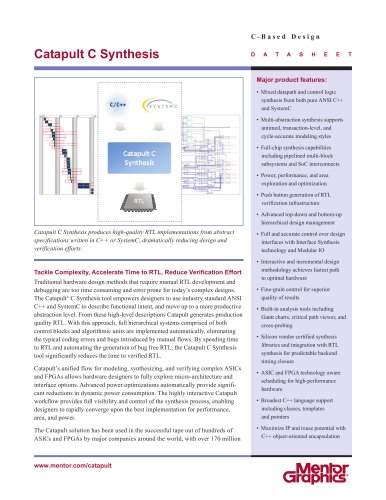

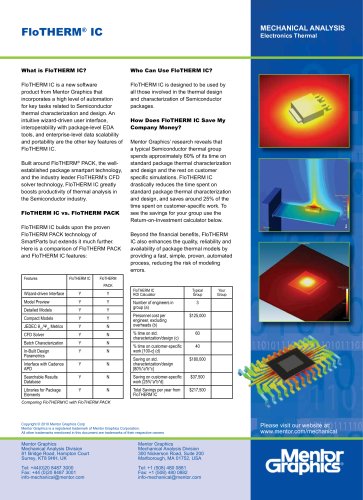

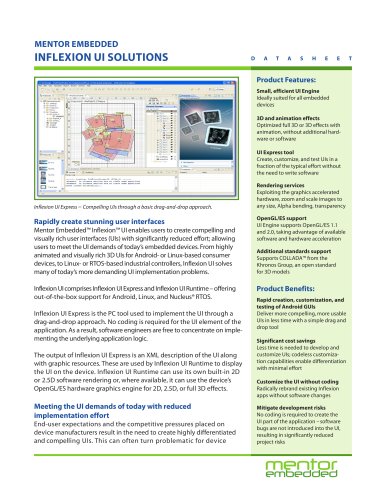

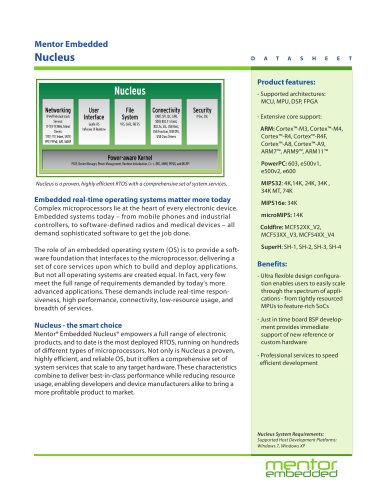

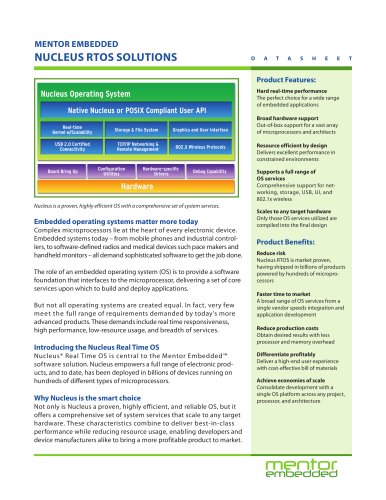

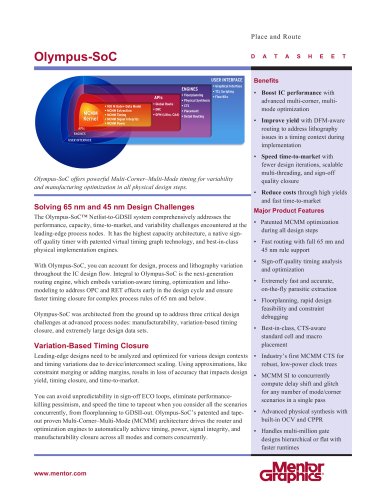

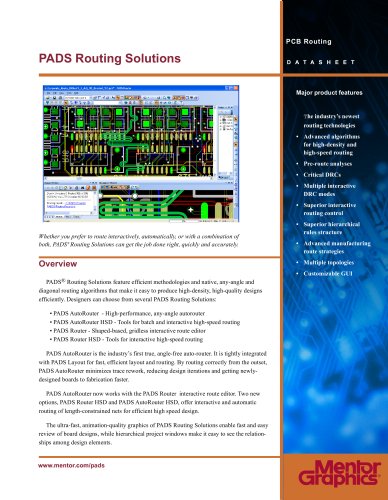

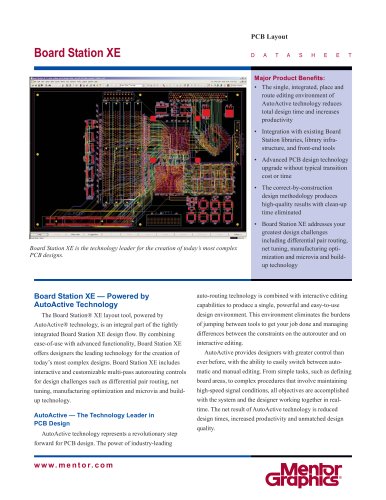

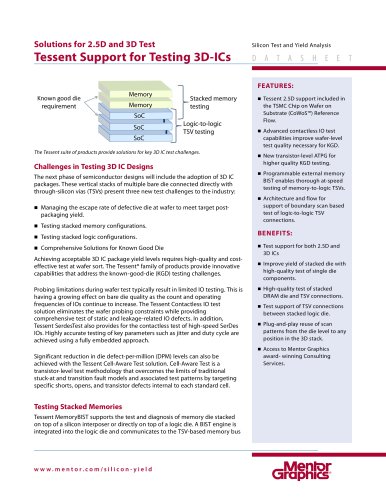

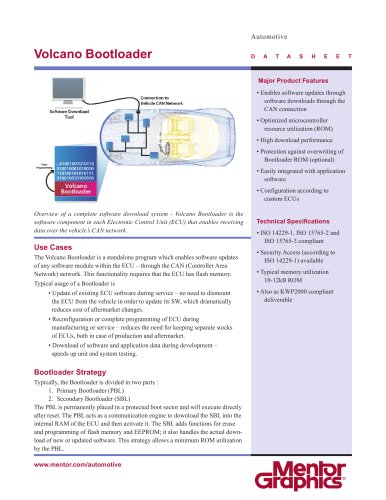

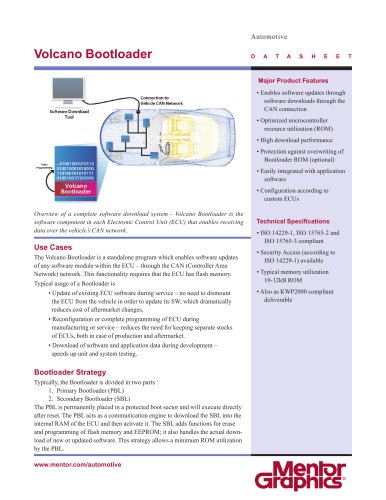

Calibre offers easy to use process modeling and tool setup, with production-

worthy accuracy and enhanced turn-around-time. The Calibre WORKbench

screen above shows some of the modeling and graphing tools. The highly

accurate Calibre simulation (lower right) matches the SEM (Scanning

Electron Micrograph) wafer image (lower left).

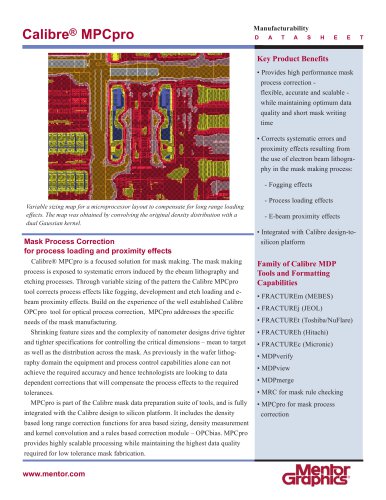

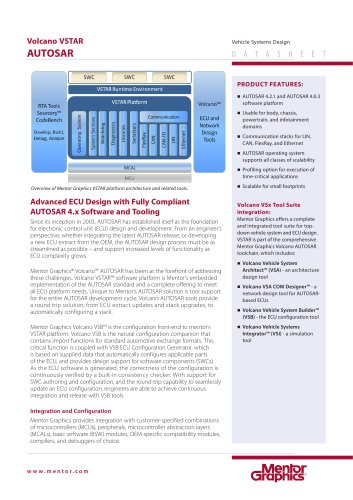

Calibre OPC and PSM: Enabling Silicon Accuracy, Speed

and Yield from 180nm to 65nm and Beyond

The Calibre product line's subwavelength tools—such as Calibre OPCpro,

Calibre ORC, Calibre PSMgate and Calibre OPCsbar—are the first complete

design-to-silicon solution. By deeply integrating OPC (optical and process

correction), PSM (phase-shift mask) and SB (scattering bar) technology with

the industry's physical verification standard, Calibre DRC and Calibre LVS, the

Calibre solution delivers silicon accuracy, fastest turn around time available,

and excellent yield. The benefits will be realized with the largest designs and

with the complexity of OPC and PSM correction layers to be reliably corrected

and verified overnight.

Key Product Benefits

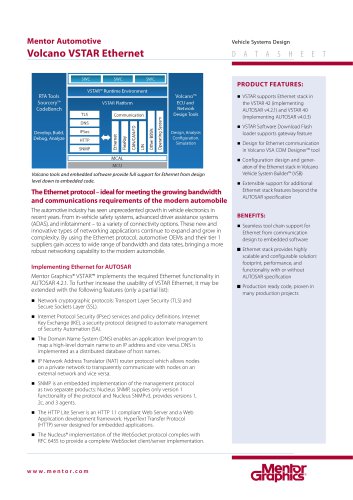

Accurate sub-wavelength

silicon: Calibre's high-NA vector

model, TCCcalc, and new process

model, VT5, will ensure unsur-

passed accuracy RET (reticle

enhancement technique) solutions.

One run, one job, one deck:

Since Calibre's sub-wavelength

tool suite is fully integrated into

Calibre's physical verification

standard, the full backend process

can be executed within a single

job deck, from post-layout to

OPC and fracture.

Decreased production costs:

Calibre's "mask-friendly" OPC

and PSM output minimizes mask

costs and lowers overall write

times.

• Flexible OPC choices: Calibre's

flexibility enables just the right

amount of OPC to be applied for

each run by offering a choice

between rule-based OPC, mini-

mizing compute intensity, and/or

model- based OPC, maximizing

correction thoroughness, even

with PSM.

• High performance chips: A

complete PSM solution enables

printing of fast, small gates and

other structures while minimizing

variances.

www.mentor.com/dsm

-Mentor

Graphics

"

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید