ADiT0 pages

AMS-Targeted Fast-SPICE Simulator

Analog/Mixed-Signal Verification

ADiT

D A T A S H E E T

FEATURES AND BENEFITS:

■ 10–100X speed improvement in

transistor-level verification of

complex AMS circuits

■ Three percent accuracy of results

by integrating SPICE and

Fast-SPICE engines

■ Over 10M device capacity

■ Seamless mixed-signal SoC

verification through integration

into Questa ADMS simulator

■ Smart partitioning algorithm

■ Default table-look up modeling

with an equation-based device

modeling option

■ Charge-conserving device models

■ Hierarchical parsing

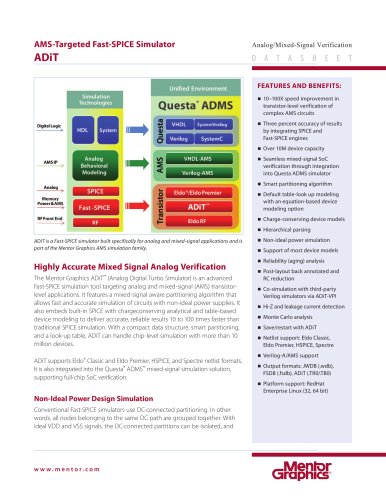

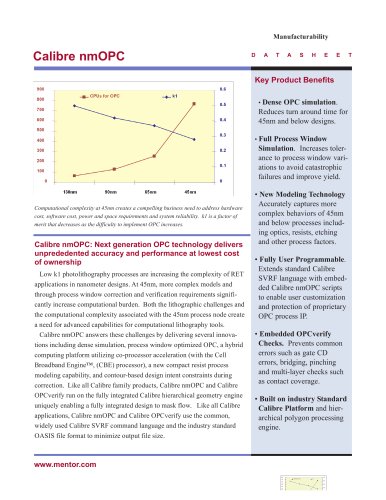

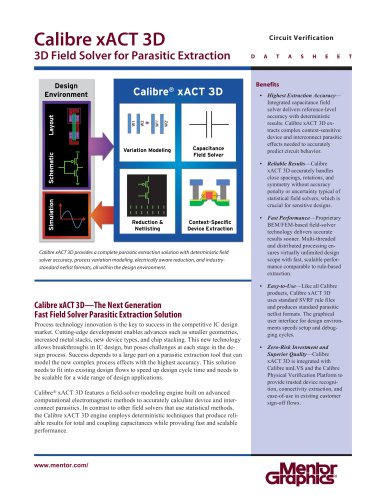

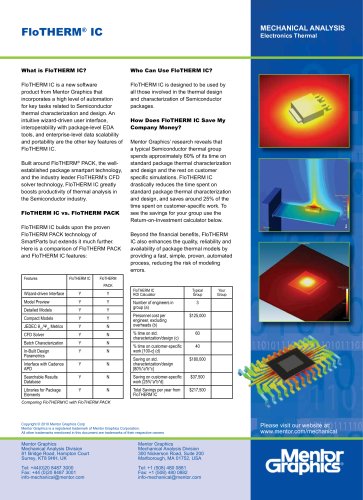

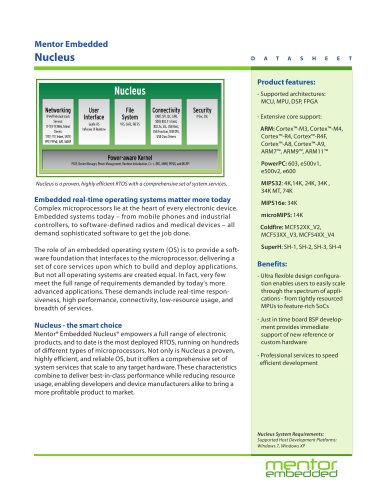

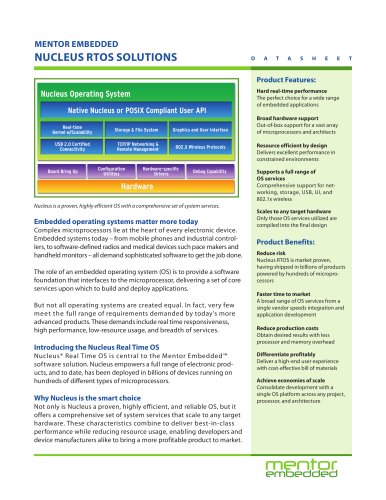

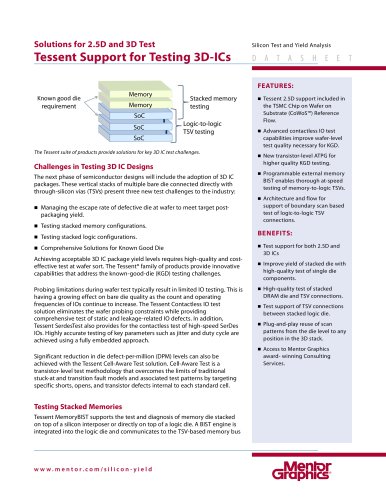

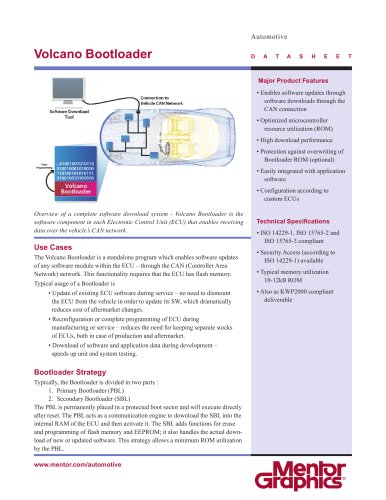

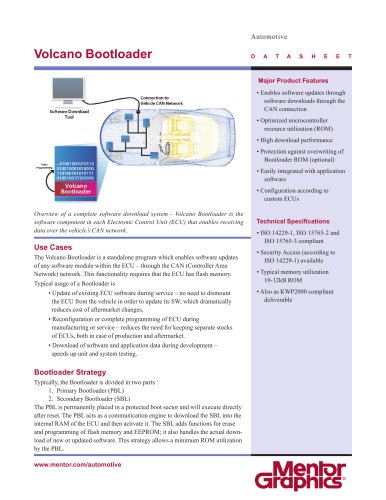

ADiT is a Fast-SPICE simulator built specifically for analog and mixed-signal applications and is

part of the Mentor Graphics AMS simulation family.

Highly Accurate Mixed Signal Analog Verification

The Mentor Graphics ADiT™ (Analog Digital Turbo Simulator) is an advanced

Fast-SPICE simulation tool targeting analog and mixed-signal (AMS) transistorlevel applications. It features a mixed-signal aware partitioning algorithm that

allows fast and accurate simulation of circuits with non-ideal power supplies. It

also embeds built-in SPICE with chargeconserving analytical and table-based

device modeling to deliver accurate, reliable results 10 to 100 times faster than

traditional SPICE simulation. With a compact data structure, smart partitioning,

and a look-up table, ADiT can handle chip-level simulation with more than 10

million devices.

ADiT supports Eldo® Classic and Eldo Premier, HSPICE, and Spectre netlist formats.

It is also integrated into the Questa® ADMS™ mixed-signal simulation solution,

supporting full-chip SoC verification.

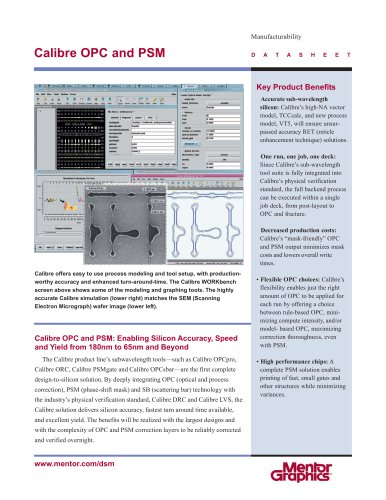

Non-Ideal Power Design Simulation

Conventional Fast-SPICE simulators use DC-connected partitioning. In other

words, all nodes belonging to the same DC path are grouped together. With

ideal VDD and VSS signals, the DC-connected partitions can be isolated, and

w w w. m e nto r. co m

■ Non-ideal power simulation

■ Support of most device models

■ Reliability (aging) analysis

■ Post-layout back annotated and

RC reduction

■ Co-simulation with third-party

Verilog simulators via ADiT-VPI

■ Hi-Z and leakage current detection

■ Monte Carlo analysis

■ Save/restart with ADiT

■ Netlist support: Eldo Classic,

Eldo Premier, HSPICE, Spectre

■ Verilog-A/AMS support

■ Output formats: JWDB (.wdb),

FSDB (.fsdb), ADiT (.TR0/.TB0)

■ Platform support: RedHat

Enterprise Linux (32, 64 bit)

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید