Calibre RealTime0 pages

^ ... _ ._. Verification

nnnnCalibre RealTime

nnnnCalibre signoff-quality verification on demand in custom/AMS design flows DATASHEET

nnnnC_eII ^iew Create Eerl iviCeii Options Query E[P Verify Placer pouter Winder DF '.

nnnna a rj m. m\ m a. a i n g a is ■*» g I ^ A a I ^ 8 w Mis!

nnnns]:1.45nm_design:XOR4D2eWP_demo:layoul[micrc-nlIJ Edit: 49]

nnnnHelp

nnnnOX- | 21 915

nnnnInstance

nnnnDY:|7

nnnnTel: |

nnnn| PreSelsc! fr

nnnn3 I_1634=Lib(lsniC_45) Cell(INRZD4BWPJ Vn^'.'.'lJ'.'Qi.it;

nnnn1 la

nnnnE

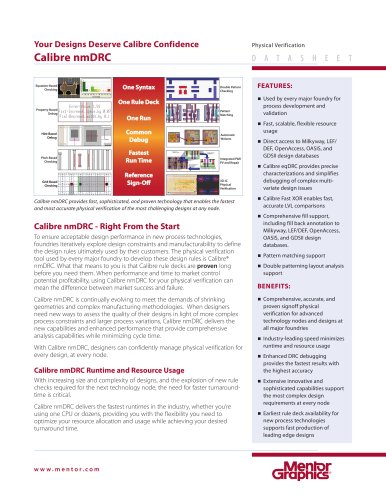

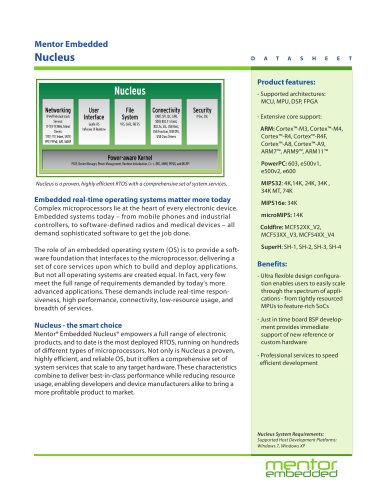

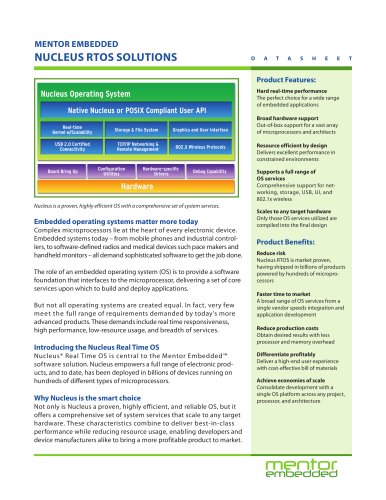

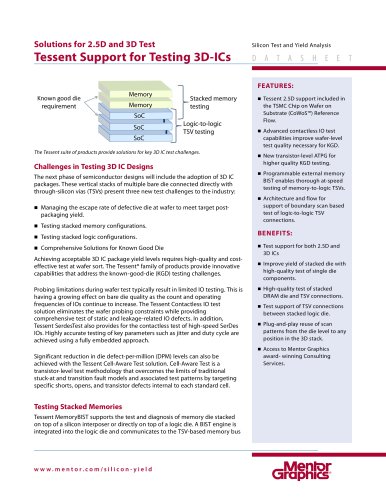

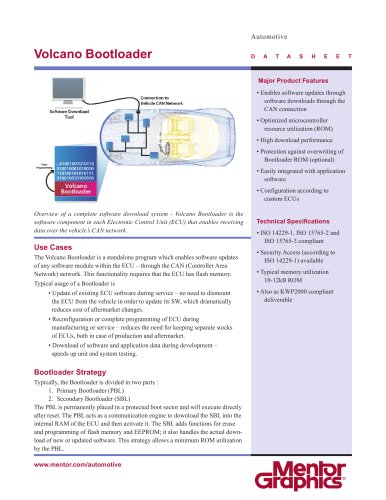

nnnnThe Calibre RealTime platform completely changes the traditional

nnnnlayout-verification-simulation loop by bringing signoff-quality verification

nnnninto the design creation process.

nnnnSignoff-Quality DRC during Design

nnnnCalibre® RealTime enables in-design signoff-quality Calibre design rule check-

nnnning (DRC) for custom and analog/mixed-signal design flows, improving both

nnnndesign speed and the quality of results by providing immediate feedback on design

nnnnrule violations and recommended rule compliance. With this information readily

nnnnavailable during layout, designers can optimize designs for increased performance

nnnnwithout incurring numerous time-consuming design-verification iterations.

nnnnBy providing the same automated check capabilities available to digital design

nnnnchecking, Calibre RealTime makes it easier for custom IC designers to produce

nnnnhigh-quality designs while still meeting production schedules. Now, no mat-

nnnnter how many drawn layers a design contains, or how many checks there are per

nnnnlayer, or even how complex those checks are, design groups working at the most

nnnnadvanced nodes can get to DRC-clean quickly and with Calibre confidence.

nnnnWhen integrated into a custom IC design and layout system, Calibre RealTime

nnnnprovides direct calls to Calibre analysis engines running foundry-qualified Calibre

nnnnrule decks. These Calibre engines perform fast, incremental checking in the vicin-

nnnnity of shapes being edited, providing nearly instantaneous feedback on design rule

nnnnviolations, as well as potential systematic variation susceptibility as measured by

nnnnrecommended rule compliance.

nnnnBenefits

nnnn• Provides instantaneous feed-

nnnnback on signoff-level DRC vio-

nnnnlations during layout creation

nnnnand editing

nnnn• Reduces verification iterations

nnnnand overall design time

nnnn• Allows interactive editing of

nnnncustom/AMS designs based on

nnnnsignoff-quality rule decks

nnnn• Enables design optimization

nnnnduring layout creation

nnnn• Integral part of design creation

nnnnflow

nnnn• Increases designer productivity

nnnnMajor Features

nnnn• Uses standard foundry-qualified

nnnnCalibre rule decks

nnnn• Built-in error review toolbar

nnnnenhances ease of use

nnnn• Automatically runs Calibre

nnnnnmDRC whenever edits are

nnnnmade

nnnn• OpenAccess run-time model

nnnnenables integration with most

nnnncustom design environments

nnnn• In-memory checking ensures

nnnnbest performance

nnnn• User-defined custom filters tied

nnnnto layout interface

nnnn• Complements existing built-in

nnnncheckers

nnnn• Award-winning

nnnnwww.mentor.com/

nnnn_Menlor

nnnnGraphics*

"

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید