Questa® Codelink Turbo0 pages

Advanced Functional Verification

Questa® Codelink Turbo

D a t a s h e e t

Major product features:

■■ Fast ARM, MIPS, and IBM PowerPC

debug visibility in HDL logic

simulations

■■ Live and Replay mode for

interactive, post-simulation debug

■■ Software source code and

hardware waveforms are fully

synchronized

■■ Multi-core support

■■ Step forward or backward through

source or assembly

■■ Source, assembly, memory,

variable, register, call-stack and

standard output views

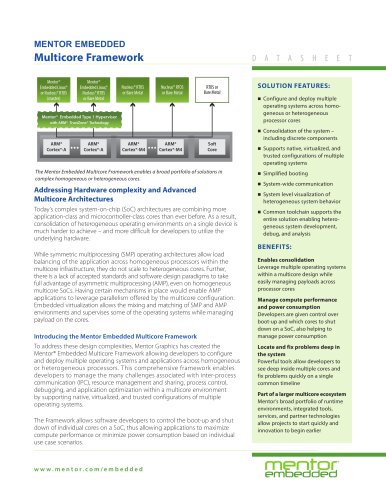

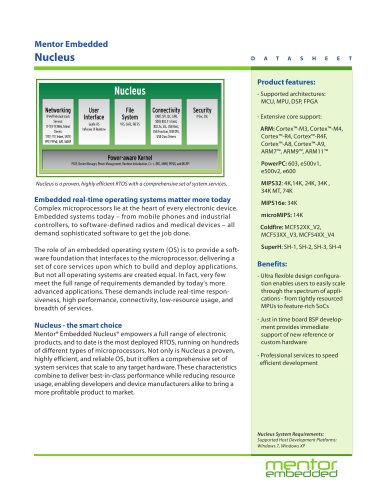

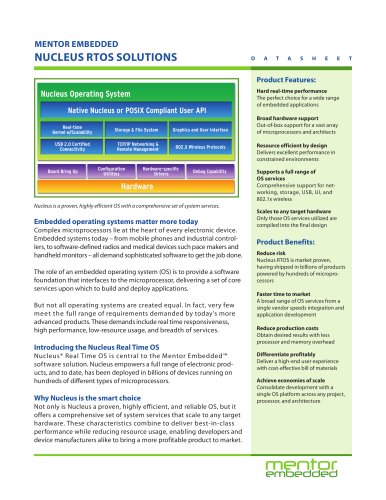

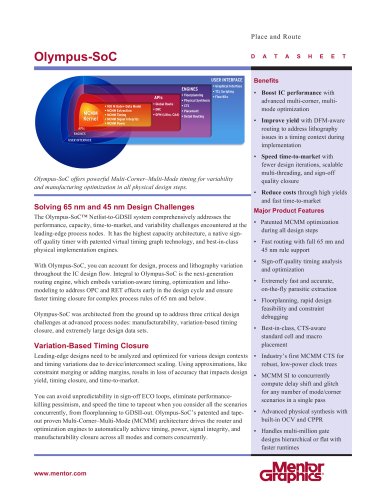

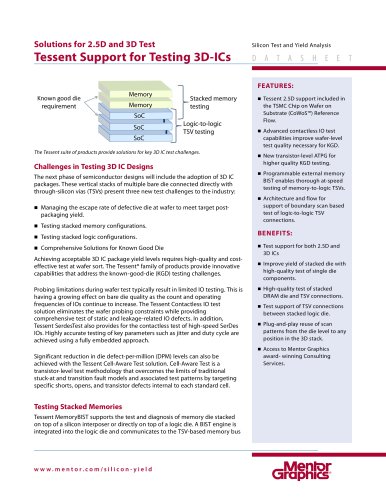

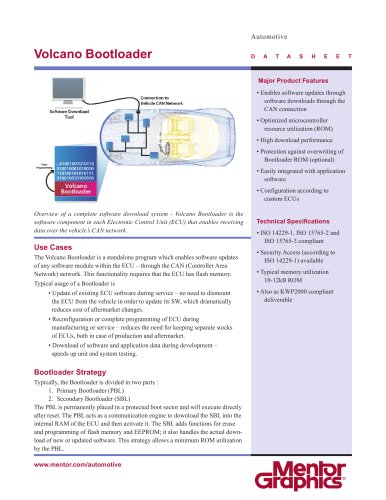

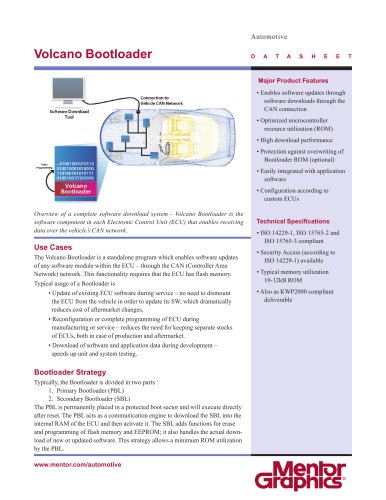

Questa® Codelink Turbo accelerates software instruction execution and provides full

processor(s) debug visibility for more efficient SoC debugging and verification.

Overview

Today’s SoC projects include embedded processors and must deliver working

embedded software and hardware. Identification of critical hardware/software

integration issues early in a project can avoid painful, time consuming,

schedule-eating defects that can derail a project’s timeline or jeopardize the

project’s quality. Using the Questa® Codelink Turbo solution, embedded

software and physical hardware arrive at system integration already having

been run together. Many defects at the hardware/software junction have

already been fixed so the project can progress quickly on the hardware

prototype. Codelink Turbo gives you confidence and reduces the risk of project

failure.

Codelink Turbo delivers speed, full visibility and control of your ARM, MIPS, and

IBM PowerPC processors while running your entire SoC design using an HDL

logic simulator. By executing embedded software on HDL-simulated hardware,

Codelink Turbo allows you to accurately debug and verify hardware/software

interactions before a hardware prototype is available. Eliminating defects in the

hardware/software interaction provides product quality while preserving or

even accelerating the project schedule. You gain confidence that the complete

product works – both the hardware and the software – early in the project

before a hardware prototype is available. Codelink Turbo’s ability to run in signoff accurate mode or fast, high performance, software execution mode, and to

dynamically switch between the two under your control, enables you to

execute significant amounts of software while retaining the fidelity of your

logic simulation environment.

w w w. m e nto r. co m /co d e li n k

■■ Four level logic (0, 1, U and X) in

the software debug windows

■■ Dynamic switch between cycle

■■ (RTL) and instruction (ISS) level of

processor’s simulation accuracy

■■ TLM interface and host mode

support

Major product benefits:

■■ Speed software execution in

simulation

■■ Debug multi-core synchronization

errors

■■ Replay overnight batch simulation

in seconds

■■ Radically reduces debug time for

tests using processors

■■ Allows RTOS boot-up in

HDLsimulation

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید