Catapult C Synthesis0 pages

C- B a s e d D e s i g n

Catapult C Synthesis D A T A S H E E T

Tackle Complexity, Accelerate Time to RTL, Reduce Verification Effort

Traditional hardware design methods that require manual RTL development and

debugging are too time consuming and error prone for today’s complex designs.

The Catapult® C Synthesis tool empowers designers to use industry standard ANSI

C++ and SystemC to describe functional intent, and move up to a more productive

abstraction level. From these high-level descriptions Catapult generates production

quality RTL. With this approach, full hierarchical systems comprised of both

control blocks and algorithmic units are implemented automatically, eliminating

the typical coding errors and bugs introduced by manual flows. By speeding time

to RTL and automating the generation of bug free RTL, the Catapult C Synthesis

tool significantly reduces the time to verified RTL.

Catapult’s unified flow for modeling, synthesizing, and verifying complex ASICs

and FPGAs allows hardware designers to fully explore micro-architecture and

interface options. Advanced power optimizations automatically provide significant

reductions in dynamic power consumption. The highly interactive Catapult

workflow provides full visibility and control of the synthesis process, enabling

designers to rapidly converge upon the best implementation for performance,

area, and power.

The Catapult solution has been used in the successful tape out of hundreds of

ASICs and FPGAs by major companies around the world, with over 170 million

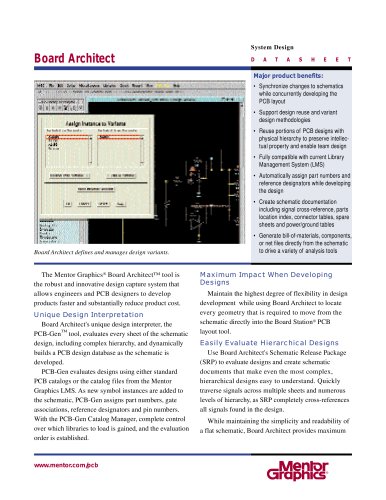

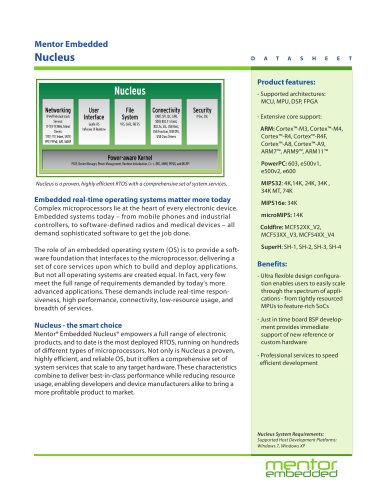

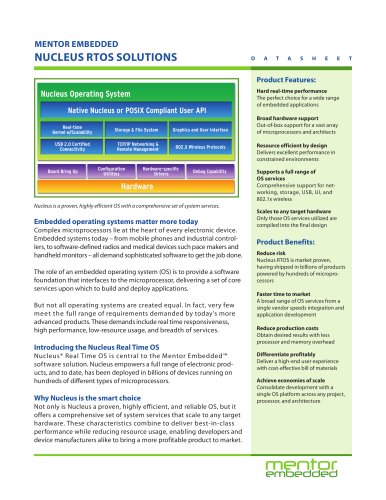

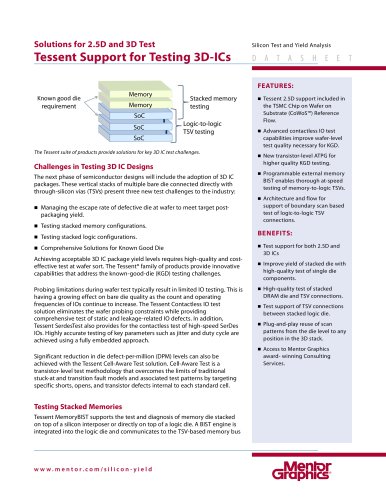

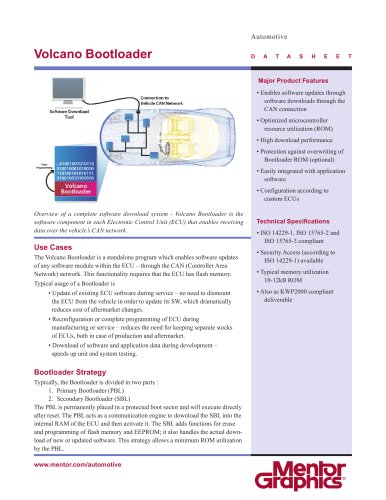

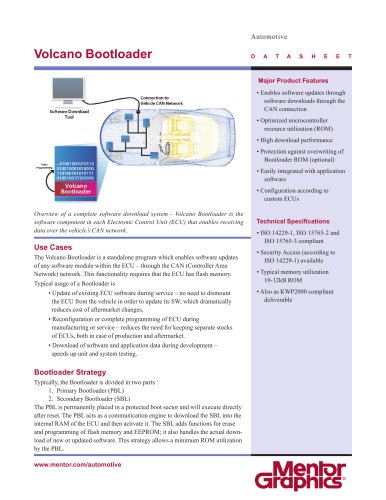

Catapult C Synthesis produces high-quality RTL implementations from abstract

specifications written in C++ or SystemC, dramatically reducing design and

verification efforts.

Major product features:

• Mixed datapath and control logic

synthesis from both pure ANSI C++

and SystemC

• Multi-abstraction synthesis supports

untimed, transaction-level, and

cycle-accurate modeling styles

• Full-chip synthesis capabilities

including pipelined multi-block

subsystems and SoC interconnects

• Power, performance, and area

exploration and optimization

• Push button generation of RTL

verification infrastructure

• Advanced top-down and bottom-up

hierarchical design management

• Full and accurate control over design

interfaces with Interface Synthesis

technology and Modular IO

• Interactive and incremental design

methodology achieves fastest path

to optimal hardware

• Fine-grain control for superior

quality of results

• Built-in analysis tools including

Gantt charts, critical path viewer, and

cross-probing

• Silicon vendor certified synthesis

libraries and integration with RTL

synthesis for predictable backend

timing closure

• ASIC and FPGA technology aware

scheduling for high-performance

hardware

• Broadest C++ language support

including classes, templates

and pointers

• Maximize IP and reuse potential with

C++ object-oriented encapsulation

www.mentor.com/catapult

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید